1 電介質材料

1、Small:具有超高儲能性能的成分和結構優化BiFeO3-SrTiO3無鉛陶瓷

介質陶瓷電容器由于其快速的充放電速度和高功率密度在先進脈沖功率器件和現代電子系統等應用領域受到越來越多的關注。然而,實際應用中如何獲得高儲能性能無鉛陶瓷是一個挑戰。

最近,同濟大學和澳大利亞伍倫貢大學的研究人員提出一種成分和結構改進策略以克服當前的挑戰。他們成功制備了BiFeO3-SrTiO3系無鉛陶瓷,并通過成分優化實現了低滯后和高極化。結果表明,兩步燒結法顯著影響了晶粒尺寸的減小和擊穿強度(EBDS)的提高,獲得了高達750 kV cm-1的EDBS值、40 μC cm-2的最大極化值和可忽略的剩余極化值(<2 μC cm?2),從而實現了8.4 J cm-3的超高能量密度和約90%的效率。能量密度和效率在1-100 Hz的頻率范圍內和直到120℃的溫度范圍內均表現出優異的穩定性,功率密度高達280 MW cm?3,這使得該BiFeO3-SrTiO3陶瓷體系在大功率儲能應用中具有潛在應用前景。相關研究工作以“Composition and Structure Optimized BiFeO3-SrTiO3 Lead-Free Ceramics with Ultrahigh Energy Storage Performance”發表于Small上。

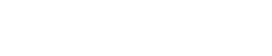

圖1. 陶瓷的電場分布、電勢分布與電樹枝演化

論文鏈接:

https://doi.org/10.1002/smll.202106515

2、NPG Asia Materials:通過乒乓式電子面積散射和界面工程獲得高能量密度BaTiO3@TiO2納米片/聚合物復合材料

介電材料由于其高穩定性和快速充放電在大功率電容器中顯示出巨大的應用潛力,但如何提高能量密度是該領域的一項長期挑戰。

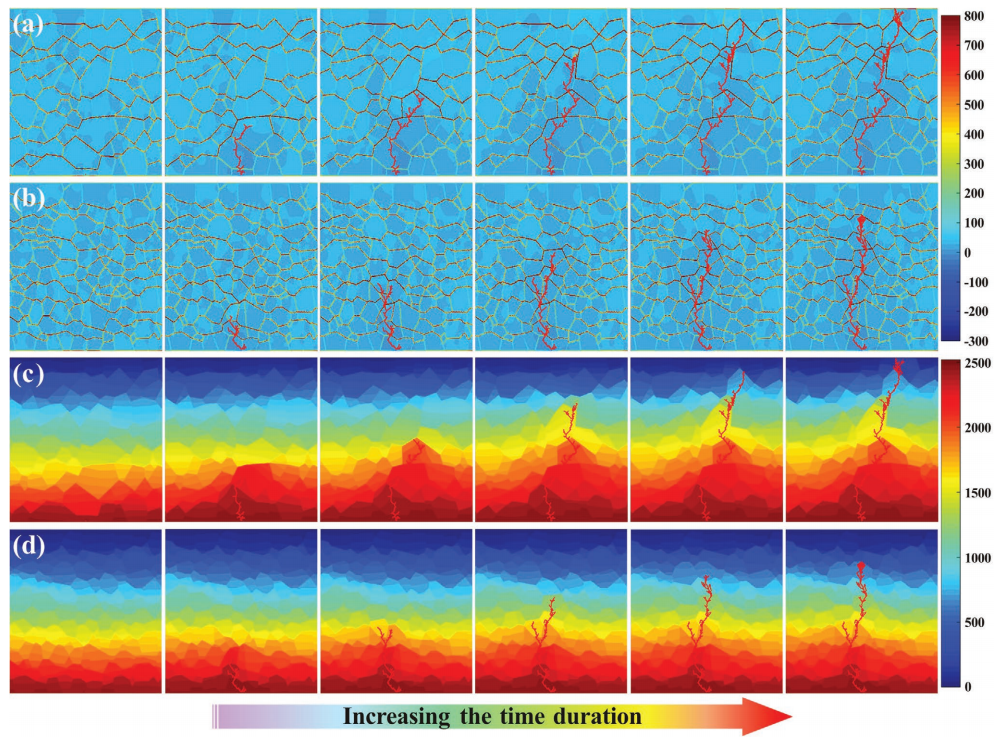

最近,江蘇科技大學和美國佐治亞理工學院的研究人員提出了一種利用殼核填料的界面和2D填料的電子散射來提高能量密度的策略,即采用鈦酸鋇納米顆粒@TiO2納米片(BT@TO ns)納米雜化物作為填料制備得到聚偏二氟乙烯(PVDF)復合材料。當填料含量為4 wt%時,這種復合材料表現出561.2 MVm?1的最大擊穿強度(Eb),比PVDF的407.6 MVm?1顯著增強?;其在1 kHz下的介電常數為12.6,比PVDF增加23%。在550 MVm?1下,獲得了21.3 J cm-3的超高能量密度和61%的效率。這種增強效應源自基于緩沖層的界面工程和2D雜化引起的增強電子面積散射,這一效應類似于乒乓球拍對電場誘導的電荷遷移的散射。這種策略可獲得用于儲能器件的高性能聚合物復合材料。該研究工作以“High energy density of BaTiO3@TiO2 nanosheet/polymer composites via ping-pong-like electron area scattering and interface engineering”發表于NPG Asia Materials上。

圖2. PVDF/BT@TO ns復合材料機理示意圖

論文鏈接:

https://www.nature.com/articles/s41427-022-00356-w

2 熱管理材料

1、Materials & Design:木質素磺酸鹽促進h-BN在纖維素基復合材料中的分散以實現可調有效熱管理

六角氮化硼(h-BN)是一種優良的導熱和電絕緣材料。然而,由于水分散性差,h-BN在熱界面材料中的傳熱路徑形成受到限制。

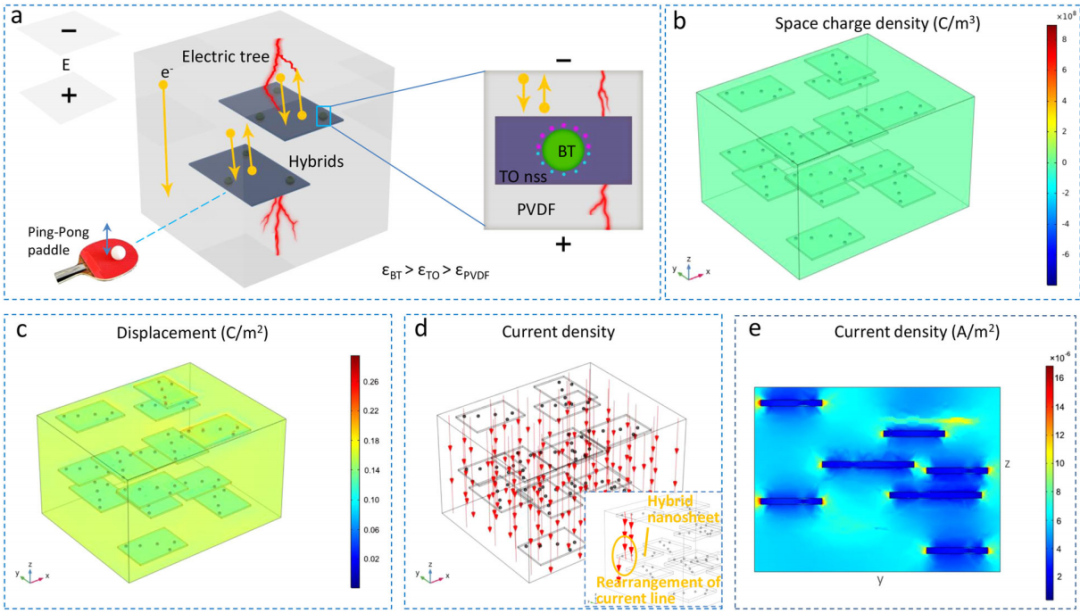

近期,南京林業大學的研究人員提出利用水溶性木質素磺酸鹽(lignosulfonate,LS)用于促進h-BN的分散,LS的酚羥基和三維結構可使其在超聲波處理下與h-BN形成氫鍵或空間位阻。與纖維素納米纖維(cellulose nanofiber,CNF)混合后,通過冷凍干燥在LS-BN/CNF氣凝膠中成功構建三維導熱路徑。結果表明,當h-BN/CNF比為3:1(w/w)時,LS含量為0.2 wt%的LS-BN/CNF/PVA復合材料的跨平面熱導率超過1.22 W/mK,是PVA薄膜(0.20 W/mK)的6.1倍。這種復合材料的初始分解溫度為205℃,拉伸強度為38.5 MPa,表現出作為熱界面和封裝材料應有的熱穩定性和機械性能。該研究為h-BN的分散提供了一條有效途徑,也為開發高性能熱界面材料鋪平了道路。這一研究成果以“Promoting h-BN dispersion in cellulose-based composite by lignosulfonate for regulatable effectual thermal management”發表于Materials & Design上。

圖3. 木質素磺酸鹽促進h-BN在纖維素基復合材料中的分散以實現可調有效熱管理

論文鏈接:

https://doi.org/10.1016/j.matdes.2021.110379

3 熱電材料

1、Nature Communications:具有寬連續成分和p型到n型可調熱電性能的類半Heusler化合物

半Heusler和全Heusler化合物被認為是具有自然成分間隙的獨立相。

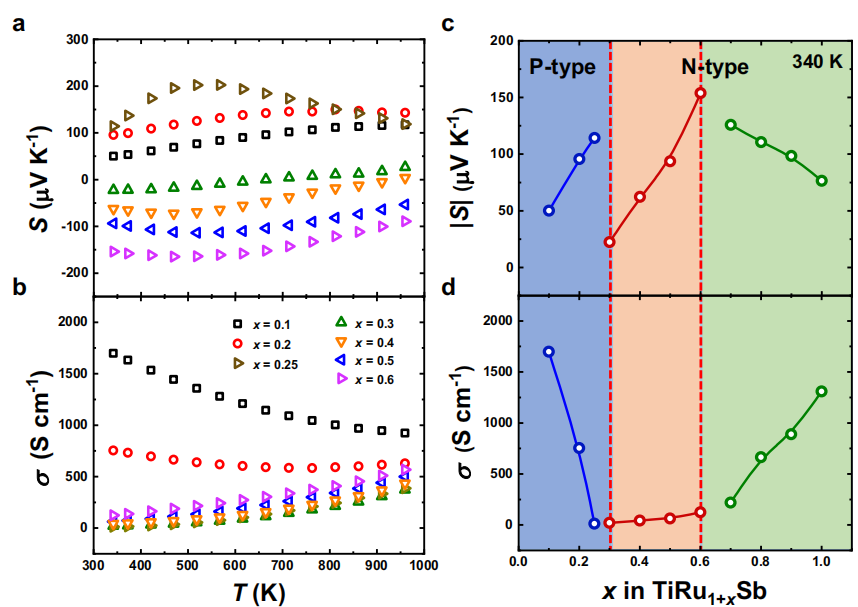

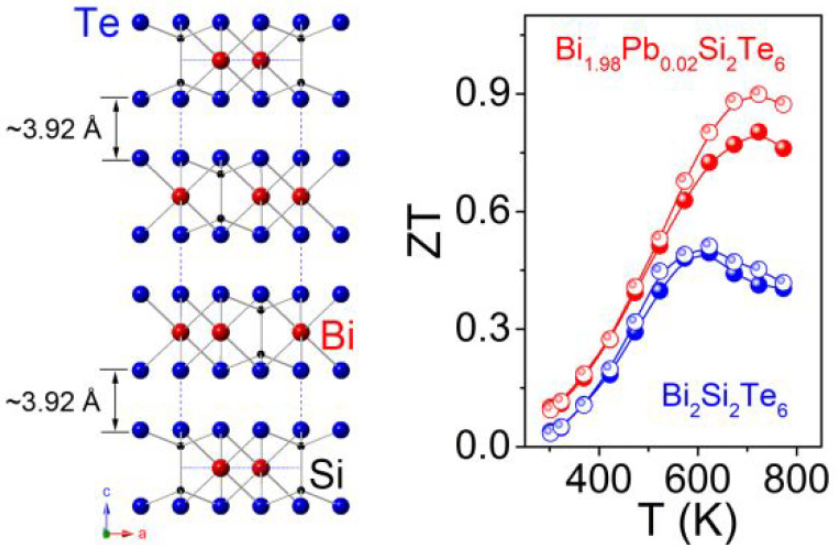

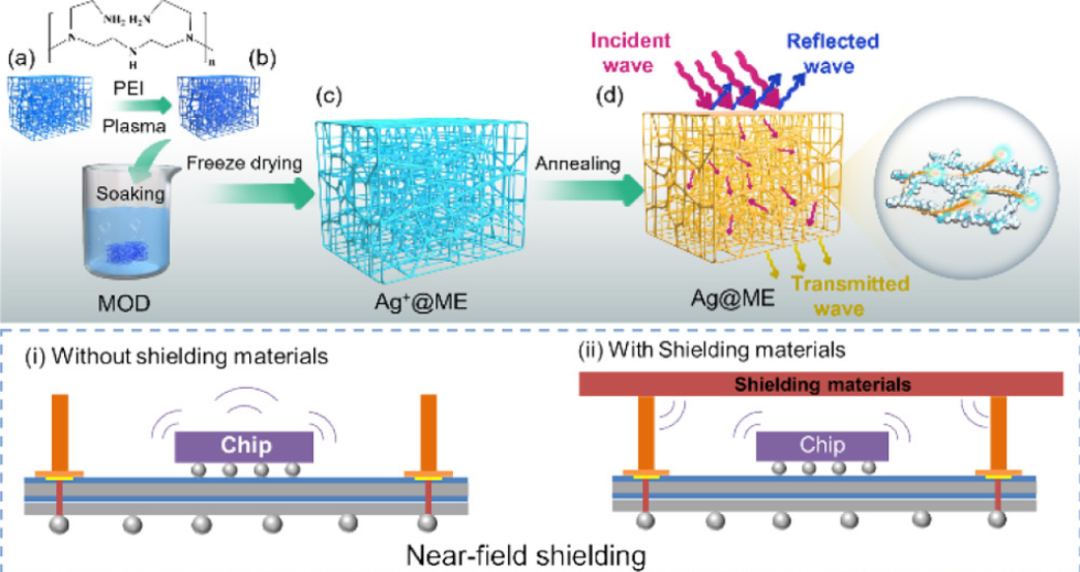

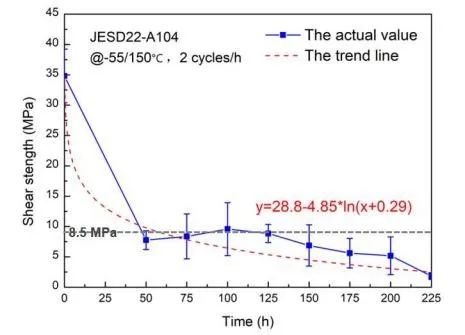

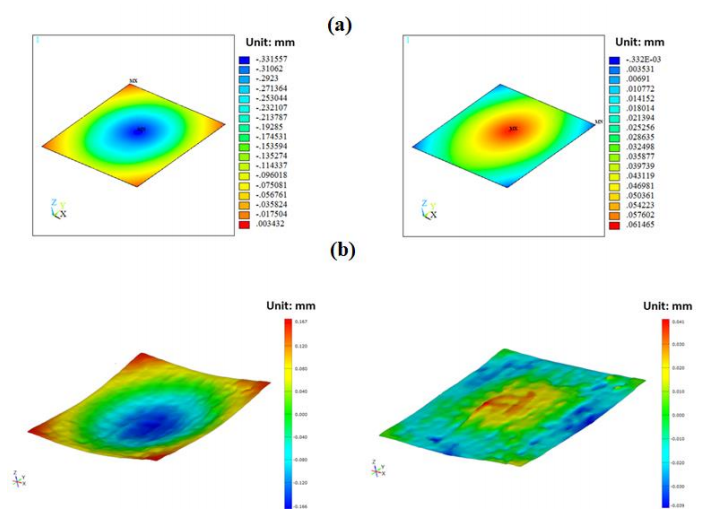

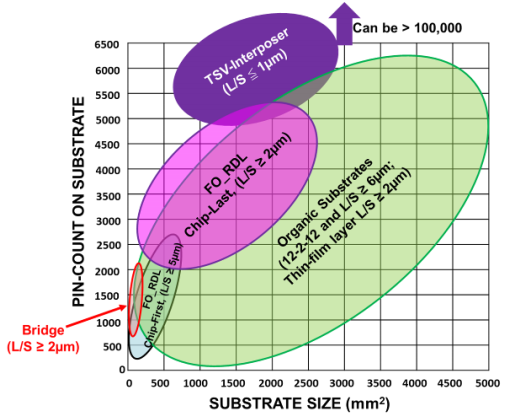

最近,南方科技大學和上海大學的研究人員報道了一種具有寬均勻性范圍和p型到n型可調熱電性能的TiRu1+xSb(x=0.15-1.0)固溶體材料,它彌合了半Heusler相和全Heusler相之間的成分間隙。在高Ru端,在TiRu1.8Sb體系中觀察到奇怪的類玻璃熱輸運行為——340 K下異常低的晶格熱導率(~1.65 W m?1K?1),這是半Heusler相報道的最低值。在0.15 圖4. TiRu1+xSb樣品的電輸運性能 論文鏈接: https://www.nature.com/articles/s41467-021-27795-3 2、J. Am. Chem. Soc.:二維Bi2Si2Te6半導體的熱電性能 Bi2Si2Te6是一種具有直接帶隙的二維半導體化合物,其光學帶隙為0.25 eV,是一種很有前途的熱電材料。 最近,美國西北大學、華中科技大學和南洋理工大學的研究人員報道了一種單相Bi2Si2Te6材料,通過可擴展的球磨和退火工藝制備,基于放電等離子燒結(spark plasmas intering)可獲得高度致密的多晶樣品。這種材料表現出p型半導體輸運行為,并具有較低的本征晶格熱導率(573 K下為0.48 W m-1 K-1,跨平面)。第一性原理密度泛函理論計算表明,這種低晶格熱導率來源于聲學聲子和低能光學聲子之間的相互作用、Bi的局部振動、低德拜溫度和獨特的二維晶體結構與介價鍵(metavalent bonding)導致的強烈非諧性。Bi2Si2Te6在623 K下的最佳熱電優值為ZT=0.51,可通過用Pb替代Bi進一步增強。由于載流子濃度的增加,Pb摻雜導致功率因數S2σ從Bi2Si2Te6的3.9μW cm–1 K–2大幅增加至Bi1.98Pb0.02Si2Te6的8.0μW cm–1 K–2(773 K)。此外,由于增強的點缺陷(PbBi’)散射,Pb摻雜導致晶格熱導率進一步降低,623 K下降低至0.38 W m-1 K-1。在同時優化功率因數和晶格熱導率的情況下,這種材料的峰值ZT值在723 K時達到0.90,400-773 K溫度范圍內的平均ZT值為0.66。相關研究工作以“Thermoelectric Performance of the 2D Bi2Si2Te6 Semiconductor”發表于J. Am. Chem. Soc.上。 圖5. 二維Bi2Si2Te6半導體的熱電性能 論文鏈接: https://doi.org/10.1021/jacs.1c12507 4 電磁屏蔽材料 1、ACS Appl. Mater. Interfaces:用于高性能EMI屏蔽的基于金屬-有機分解的聚合物泡沫金屬化骨架 航空航天、通信和大功率電子設備領域,特別是板級封裝領域,對具有輕質、柔性和高性能電磁干擾(EMI)屏蔽的高導電聚合物泡沫材料提出需求。然而,傳統的化學鍍、電鍍等制備導電聚合物泡沫材料的工藝污染嚴重,制備工藝復雜,成本高,因此迫切需要開發一種簡便易行的制備高導電聚合物泡沫的方法。 近日,深圳先進電子材料國際創新研究院的研究人員報道了一種輕質柔性的銀包覆三聚氰胺泡沫(Ag@ME),可于低溫(200℃)下在聚乙烯亞胺改性的ME骨架上通過金屬-有機分解(metal-organic decomposition,MOD)原位燒結得到。這種具有連續三維導電網絡的Ag@ME材料在2.03 vol%的體積含量下表現出良好的可壓縮性,158.4 S/m的優異導電性,以及覆蓋X、Ku、K和Ka波段(8.2-40 GHz)的寬頻EMI屏蔽效能(63 dB)。研究人員對電磁波的衰減機理進行了電磁模擬和實驗分析,并展示了這種材料在板級封裝中出色的近場屏蔽性能。這種低成本、無污染的高導電聚合物泡沫制備策略有望推動Ag@ME在電磁屏蔽領域的實際應用。相關研究成果以“Metallized Skeleton of Polymer Foam Based on Metal–Organic Decomposition for High-Performance EMI Shielding”發表于ACS Appl. Mater. Interfaces上。電子材料院芯片級封裝材料研究中心執行主任朱朋莉研究員和電磁屏蔽材料研究中心萬艷君副研究員為該論文的共同通訊作者。 圖6. 用于高性能EMI屏蔽的基于金屬-有機分解的聚合物泡沫金屬化骨架 論文鏈接: https://doi.org/10.1021/acsami.1c21836 2、J. Electron. Packag.:用于功率電子電磁干擾屏蔽的多功能磁性納米復合密封材料 隨著寬禁帶功率電子中功率密度和開關頻率的急劇增加,EMI對功率轉換效率和可靠性的影響越來越大,這就對電磁屏蔽技術提出需求。 近日,美國阿肯色大學的研究人員及其合作者開發了一種納米復合密封材料,通過將磁性氧化鐵納米顆粒直接加入硅樹脂基體中來實現電磁屏蔽。研究表明,向硅樹脂中添加少量顆粒導致EMI強度下降1.7 dBμV;然而,氧化鐵的加入使硅樹脂基體的介電擊穿強度降低了83%,這意味著若想直接應用該技術有必要進一步努力優化其介電性能。該研究證明磁性納米復合材料可能是解決功率器件電磁干擾屏蔽問題的一種潛在途徑。研究論文以“Multifunctional Magnetic Nanocomposite Encapsulant for Electromagnetic Interference Shielding in Power Electronics”發表于J. Electron. Packag.上。 圖7.如何在避免介電失效風險的情況下應用這種納米復合材料的一個示例 論文鏈接: https://doi.org/10.1115/1.4053642 5 電子封裝材料 1、J. Electron. Packag. :環氧基納米銀漿在不同無壓燒結工藝下的接頭分析及可靠性測試 近年來,低加工溫度和高工作溫度的應用需求催生了用于功率電子封裝的燒結銀膏。無壓燒結技術降低了壓力對芯片造成的應力損傷,提高了可靠性,因而在制造中得到廣泛應用。目前,大多數現有的研究都集中在醇基燒結銀漿上,而樹脂已被證明可以改善焊點的粘接性能。因此,環氧基銀漿的性能和燒結機理有待進一步研究。 最近,復旦大學的研究人員及其合作者以環氧基銀漿為研究對象,采用多因素研究的方法,揭示了其強度與不同影響因素之間的關系。通過分析商品化環氧基銀漿樣品的特性,包括銀含量、銀粒徑、有機漿料組成、樣品粘度和熱導率,在不同的無壓燒結溫度、保溫時間、基板表面和芯片尺寸下對樣品進行剪切試驗和微觀結構分析,詳細討論了全因子分析結果的相關性。研究發現,影響因素從強到弱依次為:燒結溫度、基板表面、芯片尺寸和保溫時間。最后,研究人員進行了熱循環試驗以開展可靠性分析,發現環氧樹脂殘留物是導致剪切強度呈指數下降的可能原因之一。該研究工作以“Joint Analysis and Reliability Test of Epoxy-Based Nano Silver Paste Under Different Pressure-Less Sintering Processes”發表于J. Electron. Packag.上。 圖8. 熱循環測試結果 論文鏈接: https://doi.org/10.1115/1.4053432 2、IEEE Trans. Comp. Packag. Man. Tech.:2.5D和FOCoS Chip-First、Chip-Last封裝的熱性能和力學性能表征 異質集成技術使多個單獨制造的組件集成到一個更高級別的組件中成為可能。目前,已衍生出各種類型的先進異質封裝形式,包括2.5D IC、FOCoS (Fan-Out Chip on Substrate) chip first和FOCoS chip last。 最近,臺灣虎尾科技大學和日月光半導體的研究人員構建了一種非線性模擬技術,可用于模擬上述三種封裝的翹曲、極低k(ELK)互連應力、再分布層(RDL)微應力和板級焊點可靠性。通過將FOCoS Chip-Last封裝的平面內尺寸變化數值結果與30~260℃溫度范圍內的實驗結果進行對比,驗證了仿真模型的有效性,并基于該模型分析對比了三種封裝形式的熱性能。最后,通過包含方差分析(ANOVA)的25因子設計來檢驗FOCoS Chip-Last封裝的主要結構設計參數對其典型熱負荷條件下熱機械可靠性的影響。結果表明,較薄的聚酰亞胺(PI)層有利于通過最小化PI層和RDL之間的CTE失配提高封裝可靠性。相關研究工作以“Thermal and Mechanical Characterization of 2.5D and Fan-Out Chip on Substrate Chip-First and Chip-Last Packages”發表于IEEE Trans. Comp. Packag. Man. Tech.上。 圖9. FOCoS Chip-Last封裝在30℃(左)和260℃(右)下的翹曲輪廓分布圖, (a)為模擬結果,(b)為aMA測量結果 論文鏈接: DOI: 10.1109/TCPMT.2022.3145377 3、IEEE Trans. Comp. Packag. Man. Tech.:先進封裝的最新進展和趨勢 近日,中國臺灣欣興電子股份有限公司John H Lau發表綜述文章,介紹了先進封裝的最新進展和趨勢。 在該綜述論文中,作者首先定義了先進封裝,并根據互連密度和電氣性能對各種先進封裝形式進行了排序與分類,即2D、2.1D、2.3D、2.5D和3D IC集成,并對其分別進行了介紹和討論。文章還討論了小芯片設計和異質集成封裝,它們為片上系統SoC(尤其是先進節點)提供了可行的替代方案。文章要點內容包括:(1)用于先進封裝的不同基板類型,如尺寸、引腳數、金屬線寬度和間距。(2)小芯片之間的橫向通信,例如嵌入有機增層封裝基板中的硅橋和扇出型環氧塑封料。(3)扇入型封裝,如六面成型晶圓級芯片尺寸封裝(WLCSP)等扇入式封裝及其與普通WLCSP的比較。(4)扇出型封裝,例如die face-up和die face-down的Chip-First封裝以及Chip-Last封裝,并介紹了兩者的區別。(6)面向高頻高速應用的低損耗電介質材料及其在先進封裝中的應用。(7)文章對批量回流焊、熱壓鍵合和無凸點混合鍵合等倒裝芯片組裝工藝也首次進行了簡要介紹。該綜述文章以“Recent Advances and Trends in Advanced Packaging”為題發表于IEEE Trans. Comp. Packag. Man.Tech.上。 圖10. 不同小芯片(chiplet)異質集成基板的路線圖 論文鏈接: DOI: 10.1109/TCPMT.2022.3144461 圖文 | 戰略研究辦 編輯 | 宣傳辦