跟小編一起來看看近期國內外電子材料領域都有哪些最新研究進展把~

1

科研動態

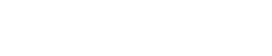

1、IEEE T. Comp. Pack. Man.:退火工藝對Ag納米層Cu鍵合質量的影響

大規模生產中,晶圓間銅鍵合的關鍵要求之一是防止銅表面氧化。

近日,首爾科技大學的研究人員提出一種策略,利用Ag納米層同時實現銅鍵合的表面抗氧化和低溫鍵合。主要評估了退火工藝對銅鍵合質量的影響。首先使用蒸鍍法在Cu表面包裹15 nm厚的Ag層,在180℃的溫度下進行30分鐘的晶圓與晶圓的銅鍵合,然后在200℃下退火60分鐘。退火過程使銅完全擴散到鍵合界面,形成均勻的純銅-銅鍵合。然而,Ag納米層沒有完全溶解到Cu薄膜中,并形成了薄的Ag帶。經過退火處理的試樣的平均剪切強度約為6.5 MPa,相對較低。盡管如此,當在銅鍵合中使用Ag納米層時,退火工藝已被證明是形成均勻鍵合界面和純銅-銅鍵合的有效方法。該文章以“Effect of the annealingprocess on Cu bonding quality using Ag nanolayer”發表于IEEE T. Comp. Pack. Man.上。

圖1. 粘接界面示意圖(a)未退火(b)200℃退火

論文鏈接:DOI:10.1109/TCPMT.2023.3278254

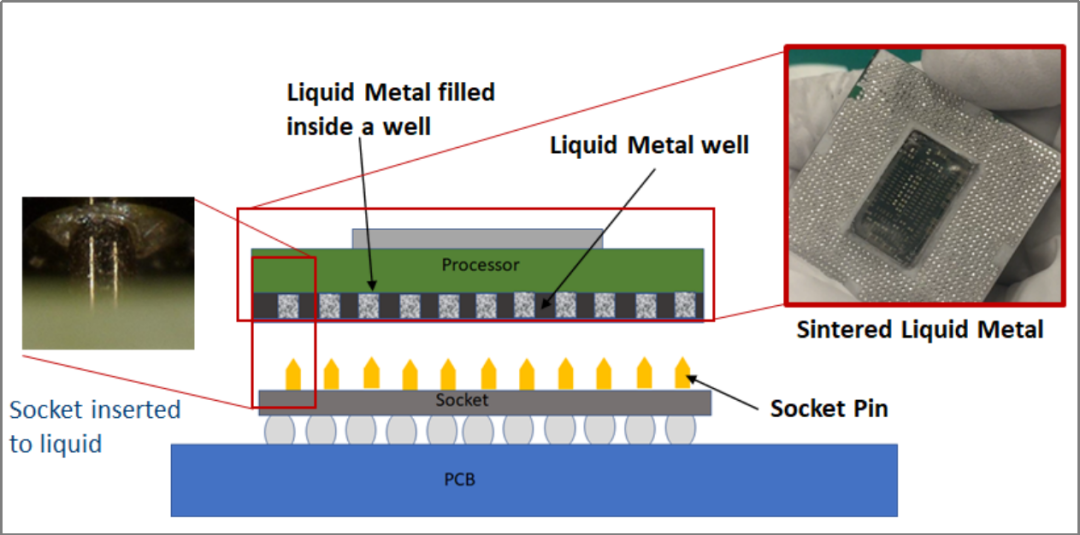

2、 IEEE T. Comp. Pack. Man.:液態金屬低電阻互連技術

人們希望互連技術能夠提供低接觸電阻、更短的電路,并且無需復雜的裝載結構即可實現引腳數縮放。球柵陣列(BGA)技術具備一定的優勢,但是在尤其是大尺寸的封裝上,增加了表面貼裝挑戰的復雜性。此外,客戶看重插座(socket)的可分離連接的靈活性。然而,插座的高接觸電阻和所需的加工壓力會顯著提升裝載結構的成本和復雜性。

近日,英特爾公司的研究人員介紹了一種基于液態金屬的插座互連技術。該技術可提供類似BGA的性能,同時具有傳統插座的優點。實驗研究的液態金屬是一種低熔點的鎵基共晶合金。測得的接觸電阻是所有插座技術中最低的,與永久焊點連接接近。文章還介紹了制造液態金屬互連的工藝及其電特性。值得注意的是,傳統的評估方法難以評價這種新型互連,因此同時還引入了新的評估方法。由于該技術尚處于起步階段,可靠性風險或潛在故障機制的研究數據還不不充分。該研究為新型互聯技術提供了新的思路。該文章以“Liquid Metal Based Low Resistance Interconnect Technology”發表于IEEE T. Comp. Pack. Man.上。

圖2. 插入液態金屬和插座引腳的臺式處理器

論文鏈接:DOI:10.1109/TCPMT.2023.3274743

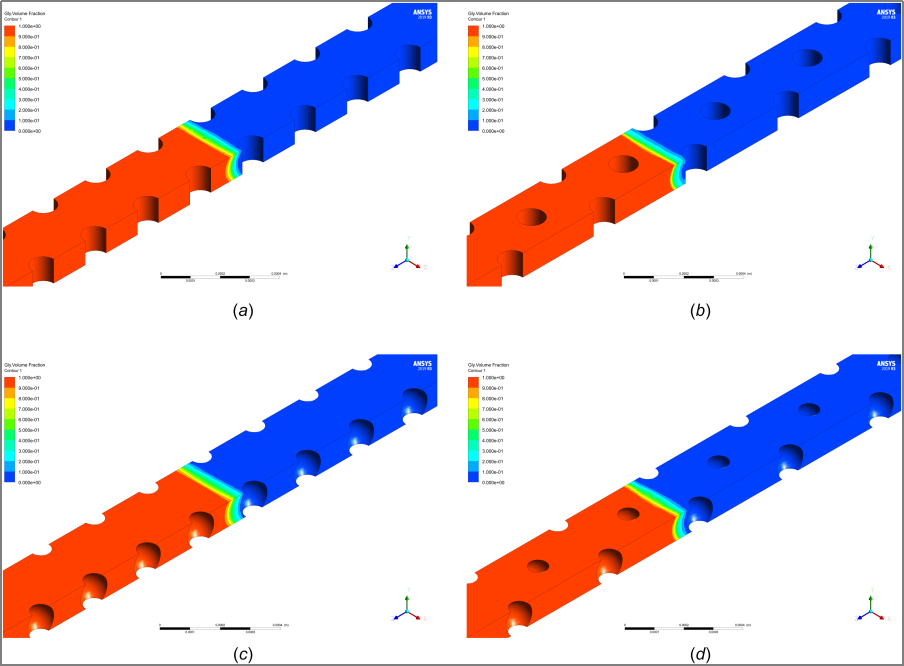

3、J. Electron. Packaging:基于表面能的倒裝封裝底部填充流動過程分析模型的方法開發

倒裝封裝是一種廣泛應用的先進封裝技術,底部填充材料的主要作用是減少芯片和基板之間的應力,避免焊點失效。準確的數學模型有助于更好的理解和控制底部填充過程。

近日,華東理工大學等機構的研究人員提出了一種建立倒裝封裝中底部填充過程分析模型的方法,基于表面能概念和能量守恒原理,預測流動前峰(flow front)和填充時間。該方法不需要對流動路徑建模,因此適用于不同的焊點布局情況,包括倒裝封裝中焊點不同的形狀和排列方式。為驗證該方法的有效性,實驗人員在自行開發的試驗臺上進行了計算流體力學的模擬實驗。實驗和仿真結果表明,該方法及其模型對于具有不同焊點結構和布局的倒裝芯片封裝都是準確的。該工作為芯片底部填充材料的研發提供了參考。該文章以“A Surface Energy Approach to Developing an Analytical Model for the Underfill Flow Process in Flip-Chip Packagin”發表于J. Electron. Packaging上。

圖3. 單通道底部填充過程的流體力學仿真

(a)方形排列圓柱形焊點(b)正三角形排列圓柱形焊點

(c)方形排列球形焊點(d)正三角形排列圓柱形焊點

論文鏈接:https://doi.org/10.1115/1.4052275

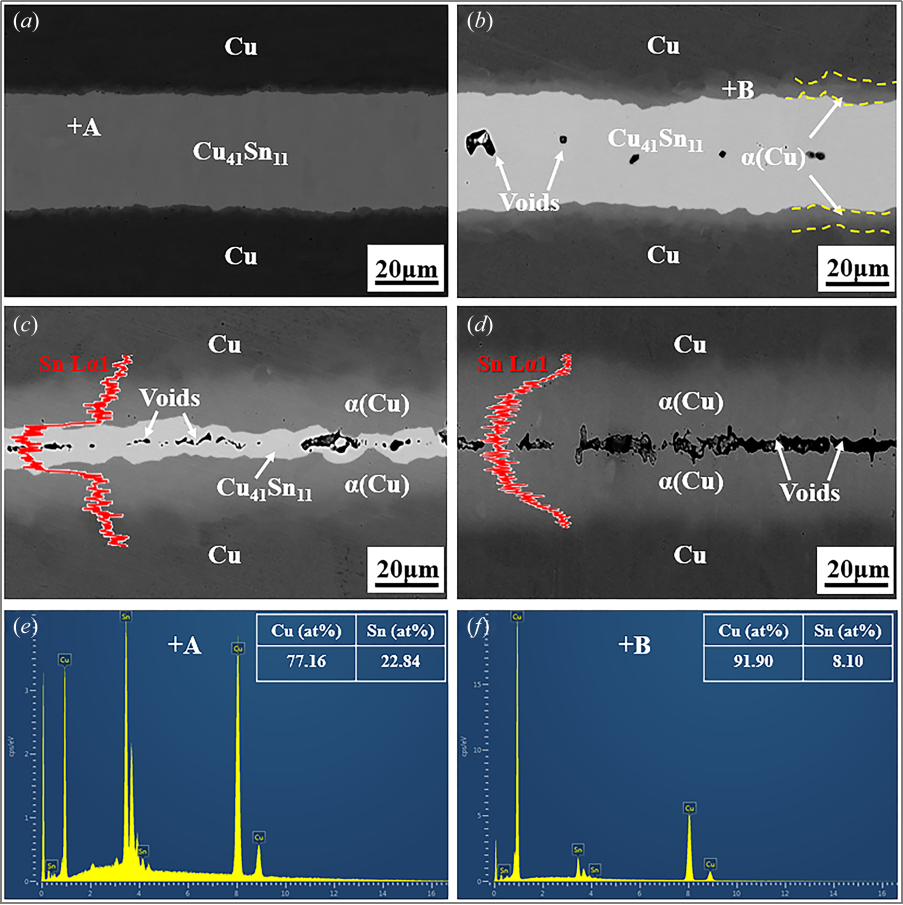

4、J. Electron. Packaging:Cu/Cu41Sn11/Cu焊點在高溫老化過程中的微觀結構演變和力學性能研究

焊點作為連接芯片和載板的橋梁,它不僅提供機械支撐和物理保護,還具有集成電路的信號傳輸和熱冷卻功能。這意味著焊點的可靠性在電子產品的性能中起著至關重要的作用。

近日,北京工業大學的研究人員對全Cu41Sn11焊點(Cu/Cu41Sn11/Cu)在420℃等溫老化過程中的微觀結構和機械性能變化進行了研究。實驗結果表明,Cu41Sn11相在高溫條件下是不穩定的,在溫度老化進行到150 h時,全Cu41Sn11焊點轉變為全α(Cu)焊點(Cu/α(Cu)/Cu)。形成的α(Cu)相是Sn原子濃度不均勻的Cu固溶體,其晶體結構和取向與原始Cu盤一致。Cu41Sn11向α(Cu)的轉化過程中,在焊點界面的中間部分附近,由于體積收縮效應形成了空隙。與Cu41Sn11焊點相比,α(Cu)焊點的強度有所下降,但應變速率敏指數有所上升。此外,α(Cu)和Cu41Sn11的應變速率敏感指數低于普通Sn焊料。剪切試驗中Cu41Sn11晶粒中發生的斷裂是脆性的,而α(Cu)晶粒中的斷裂是韌性的。該研究為Cu-Sn金屬間化合物(IMCs)焊點在第三代寬帶隙半導體器件中的潛在應用提供了指導。該文章以“Study on the Microstructure Evolution and Mechanical Properties of Cu/ Cu41Sn11/Cu Solder Joint During High-Temperature Aging”發表于J. Electron. Packaging上。

圖4. 420℃不同老化時間下全Cu41Sn11焊點的截面微觀結構:

(a)0?h、(b)20?h、(c)100?h、(d)150?h、(e)和(f)A、B點EDS結果

2

行業動態

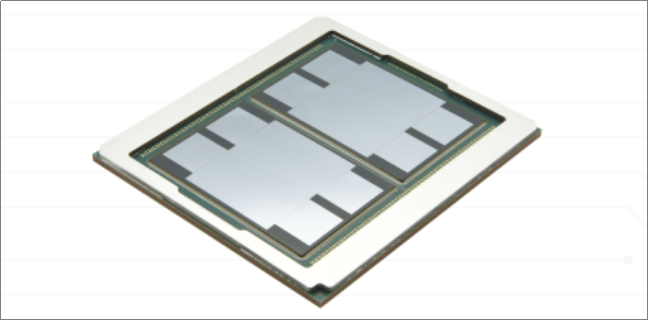

1、日月光(ASE)扇出型基板橋接(FOCoS-Bridge)封裝

越來越多的行業和學科已經涉及到人工智能的使用,高性能計算(HPC)同時也對創新型先進封裝提出了需求。

近日,ASE開發了一種扇出型基板橋接(FOCoS-Bridge)封裝,該封裝技術利用高度集成的扇出結構來克服傳統電器互聯的局限性,并實現處理器、加速器和內存等模塊之間高速、低延遲和高效能的數據通信。在70×78 mm的FOCoS-Bridge封裝中,ASE使用一種硅橋技術實現Chiplet集成,該技術利用具有布線層的微小硅片作為芯粒之間的封裝內互聯。封裝結構中包含2個ASIC和8個通過硅橋連接的高帶寬儲存器件(HBM),也就是在大的封裝結構內,并排集成了兩個相同的47×31 mm FOCoS-Bridge結構,每個結構分別包含1個ASIC、4個存儲器件和4個硅橋。

圖5. FOCoS-Bridge封裝結構外觀示意圖

FOCoS-Bridge封裝的制造工藝

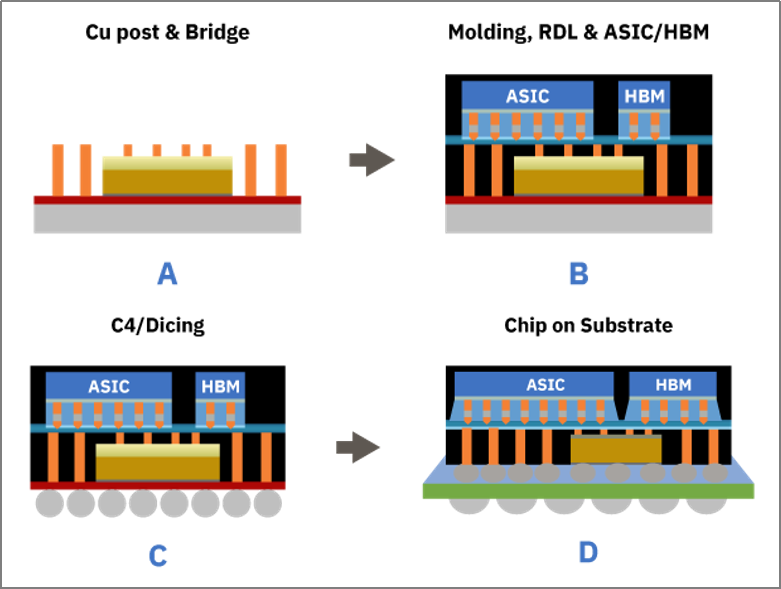

首先,將待嵌入的帶有微凸塊的硅橋芯片連接到晶圓載體上,然后在晶圓載體上鍍銅柱(圖6A)。隨后進行第一次塑封加工,將塑封后的產品研磨以露出Cu柱和微凸塊,然后在其上形成RDL層,之后再連接ASIC和HBM,進行底部填充和成型(圖6B)。移除晶圓載體并形成C4凸塊后,將模制晶圓切割成單獨的扇出封裝(圖6C)。最后,使用常規倒裝芯片工藝將扇出封裝連接到有機基板上(圖6D)。

圖6. FOCoS-Bridge封裝的制造工藝流程示意圖

FOCoS-Bridge封裝的優勢

FOCoS-Bridge被定位為使用硅中介層的2.5D封裝的替代品。與2.5D封裝一樣,硅橋在封裝中提供超細間距互連,可以解決系統中的內存帶寬瓶頸挑戰。與2.5D相比,FOCoS-Bridge的優勢在于只在兩個芯粒連接在一起的區域使用硅片。

FOCoS-Bridge技術能實現與硅中介層的類似性能,但成本更低,且具有高度可擴展性,能夠無縫集成到高性能計算和人工智能應用中使用的復雜Chiplet架構中。它提供高密度芯片到芯片連接、高 I/O 數量和快速信號傳輸。使用硅橋芯片可實現比傳統有機倒裝芯片封裝高一個數量級的芯片邊緣線性密度。

此外,FOCoS-Bridge為在扇出封裝中嵌入無源器件和有源芯片奠定了基礎,有助于更有效地利用計算資源,加速數據密集型工作負載,并有助于推進AI算法、深度學習、科學模擬和其他計算要求苛刻的任務。

(Source:EDN、ASE)