1、Adv. Mater.:用于3D電子封裝的內部設計高導熱通路的微結構氮化硼復合材料

小型化和高功率密度的3D電子設備對熱管理提出了新的挑戰。目前,絕緣封裝中的散熱效率受到熱界面材料(TIM)的熱導率及其將熱量傳遞至散熱器能力的限制。近日,新加坡南洋理工大學等機構的研究人員使用磁輔助滑動鑄造得到一種高導熱氮化硼(BN)基復合材料,該復合材料能夠通過局部定向磁性功能化的BN微板來有針對性地向特定區域導熱。由于復合材料中的BN含量高達62.6 vol%并且排列度較高、而聚合物粘合劑的含量較低,導致沿排列方向的熱導率高達12.1 W m?1 K?1。同時,該BN復合材料密度低至1.3 g cm?3、硬度高達442.3 MPa,并且是絕緣的。該工作合理設計TIM的微觀結構,有策略地進行導熱,為3D集成電子中的有效熱管理提供了一個有前途的解決方案。該文章以“Microstructured BN composites with internally designed high thermal conductivity paths for 3D electronic packaging”發表于Adv. Mater.上。

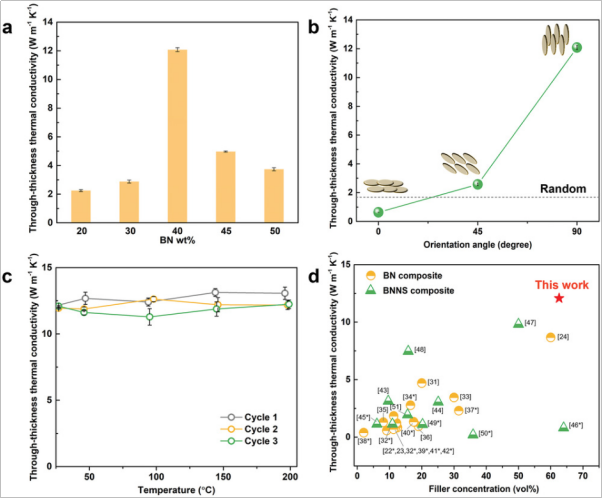

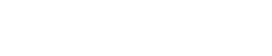

圖1. (a)熱導率與BN濃度關系(b)不同取向角度與隨機排列復合材料比較

(c)溫循下的熱穩定性(d)本工作與其他文獻報道的各種BN復合材料比較

論文鏈接:https://doi.org/10.1002/adma.202205120

2、 Nano Letters:粘附能可以優化軟/硬材料界面熱阻嗎?

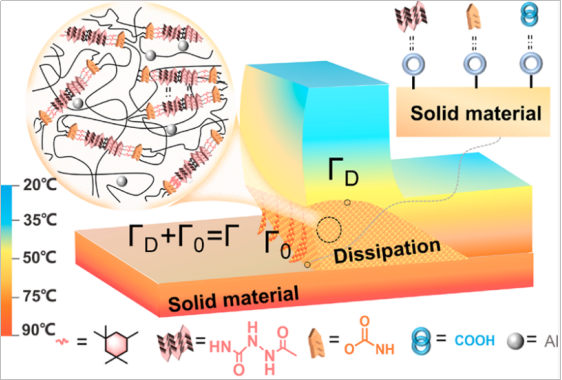

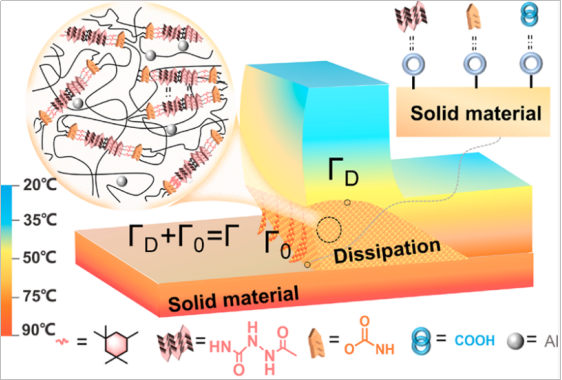

軟/硬材料界面熱阻在電子封裝、傳感器和醫學的發展中發揮著重要的作用。粘附能和聲子譜匹配是決定界面熱阻(ITR)的兩個關鍵參數,但在一個系統中很難通過同時實現這兩個參數來降低軟/硬材料界面熱阻。近日,深圳先進電子材料國際創新研究院等機構的研究人員設計了一種由聚氨酯-硫辛酸共聚物和微米級球形鋁組成的彈性體復合材料。該復合材料與硬質材料表現出高度聲子譜匹配和高粘附能(>1000 J/m2),從而實現了0.03 mm2·K/W的低界面熱阻。在此基礎上,該團隊進一步開發出關聯粘附能和ITR的定量物理模型,以揭示粘附能的關鍵作用。這項工作有助于從粘附能的角度設計軟/硬材料界面熱阻,將推動界面科學發展的范式轉變。該文章以“Can Adhesion Energy Optimize Interface Thermal Resistance at a Soft/Hard Material Interface”發表于Nano Letters上。深圳先進電子材料國際創新研究院熱管理材料研究中心碩士研究生程霞霞為該論文的第一作者,曾小亮研究員和王淑婷博士后為共同通訊作者。

圖2. 復合材料設計原理和表觀粘附能、固有粘附能和能量耗散之間的關系

論文鏈接:https://doi.org/10.1021/acs.nanolett.3c01882

3、 J. Electron. Packaging:燒結納米銅接頭的有效本構關系

燒結納米銅被認為是焊料和燒結銀的替代品,因此,需要對其加速疲勞失效結果進行建模,包括基于本構關系預測應力和應變與溫度之間的關系。然而這帶來了一個挑戰,因為非彈性形變特性與初始顆粒和加工細節強相關。

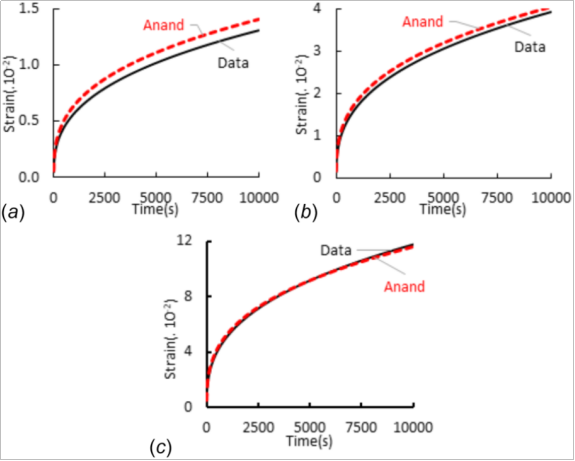

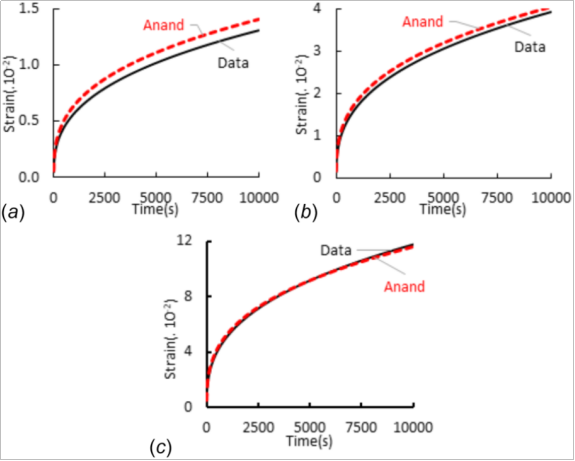

近日,賓漢姆頓大學等機構的研究人員提供了與循環相關的早期瞬態蠕變的機制描述,包括燒結參數和隨后氧化的影響。發現非彈性變形以擴散為主,而非位錯運動。并提出了廣義本構關系,使得特定結構的定量建模只需要測量單個蠕變曲線。該工作為燒結納米銅的研發提供了參考。該文章以“Effective Constitutive Relations for Sintered Nano Copper Joints”發表于J. Electron. Packaging上。

圖3. 使用Anand模型在(a)10 MPa(b)30 MPa(c)90 MPa應力下,實際應變數據與計算的比較 論文鏈接:https://doi.org/10.1115/1.4056113

4、 J. Electron. Packaging:無鉛焊點的剪切和疲勞特性:建模和微觀結構分析

在電子行業禁止使用鉛后,由于低溫焊料(LTS)合金的成本較低,且減少了復雜組件中的缺陷,最近受到了廣泛的關注,因此Sn-Ag-Cu(SAC)基焊料合金的可靠性也得到了廣泛的研究。

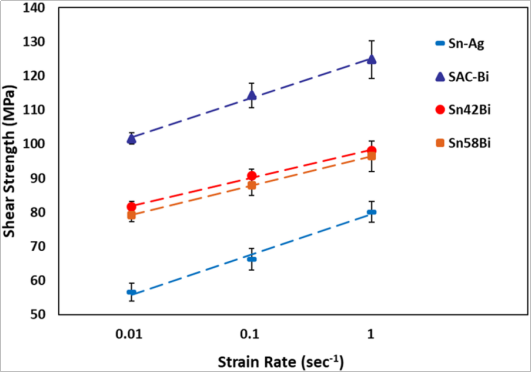

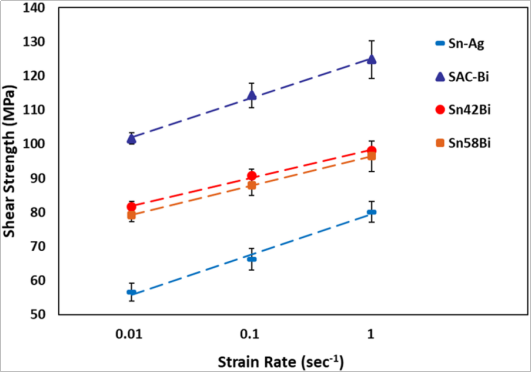

近日,奧本大學等機構的研究人員測試了兩種新型低熔點焊料合金(Sn-58Bi-0.5Sb-0.15Ni和Sn-42Bi)單個焊點的剪切和疲勞性能,并與Sn-3.5Ag和Sn-3.0Ag-0.8Cu-3.0Bi進行了比較。在三種應變速率下進行剪切試驗,并測量每種焊料合金的剪切強度,其中循環疲勞試驗采用恒定應變速率,針對不同的應力幅度確定了每種合金的疲勞壽命。并對剪切和疲勞試驗中的失效機制進行了表征,結果表明,與其他合金相比,Sn-3.0Ag-0.8Cu-3.0Bi具有優異的剪切和疲勞性能,但更容易發生脆性破壞;剪切應變速率影響Sn-3.0Ag-0.8Cu-3.0Bi、Sn-58Bi-0.5Sb-0.15Ni和Sn-42Bi的失效模式,但對Sn-3.5Ag影響不明顯。該研究為新型低熔點焊料合金的開發提供了指導。該文章以“Shear and Fatigue Properties of Lead-Free Solder Joints: Modeling and Microstructure Analysis”發表于J. Electron. Packaging上。

圖4. 四種焊料合金的平均剪切強度與不同剪切應變率的關系論文鏈接:https://doi.org/10.1115/1.4055318

1、 IMEC sub-1 nm制程藍圖中的4項重要技術概述

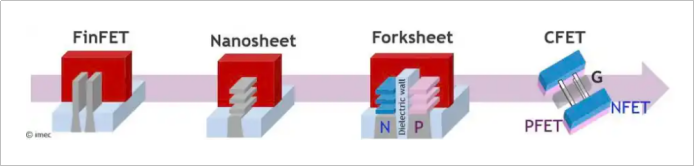

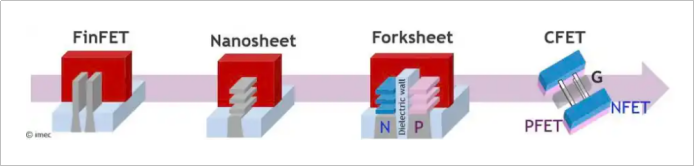

近日,作為世界上最先進的半導體研究機構,IMEC在比利時舉行的ITF世界活動中分享了其1 nm以下制程的工藝路線圖,展示了對應的晶體管架構研究和開發計劃。同時,IMEC認為人工智能和機器學習所需要的原始計算能力大約每6個月會翻一倍。該活動還強調,每一代的芯片的基礎問題都變得越來越棘手,比如互聯帶寬的限制已經嚴重滯后,阻礙了CPU、GPU等性能提升。以下是IMEC認為能起到主導作用的4項技術,其中持續收縮的芯片互連以及3D堆疊設計,對推動1 nm以下的工藝節點尤為關鍵。雖然標準的FinFET晶體管技術將持續到3 nm節點,但在2024年將被新的GAA(gate all around)納米片制造技術大批量取代。GAA技術使用與多個鰭片相同的驅動電流,有助于提高晶體管密度和性能。根據IMEC的技術路線圖,叉片晶體管是GAA的更密集版本,將從2 nm節點開始進入,最終突破0.7 nm。另外,CFET(complementary FET)技術預計在2028年達到1 nm制程,進一步縮小晶體管尺寸。同時CFET晶體管將NMOS和PMOS堆疊在一起,實現更高密度。以及其他的一些CFET的版本,將實現0.5和0.2 nm節點。

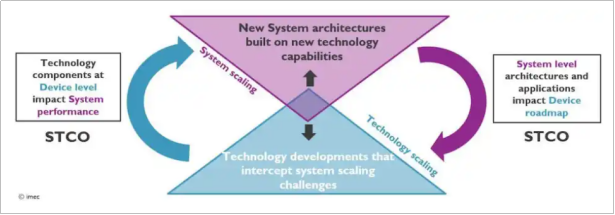

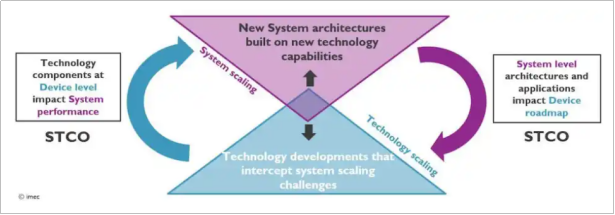

圖5. 芯片制造技術可能在近十年內從FinFET發展到CFET系統技術協同優化(STCO)是一種設計方法,將單片芯片的功能單元(如緩存、I/O和供電)分解,以針對所需要的性能使用不同的晶體管對各單元進行優化。分解的目的之一是為了能在3D堆疊中將緩存和內存拆分為不同的層,為實現該目的同時還要求IC堆疊的頂部復雜性盡量降低。IMEC指出應改進后端(BEOL)工藝,將晶體管連接在一起,實現芯片信號傳輸和供電。

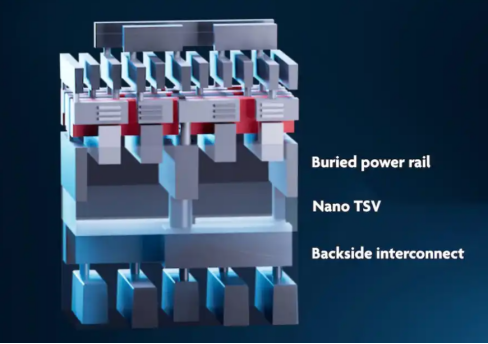

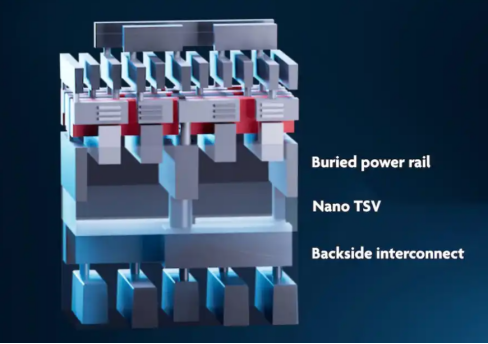

背面供電(backside power distribution networks,BPDN)技術是指通過晶體管的背面進行電傳輸,該技術將在2024年隨著2 nm制程首發。該項技術最大的特點是將供電電路和數據傳輸分開,因此壓降特性得到改善,也使得芯片頂部能進行更高密度信號傳輸。同時,供電網絡轉移到芯片底部后,芯片頂部也可以更容易的進行晶圓與晶圓之間的鍵合,讓在存儲芯片上堆疊邏輯芯片成為可能。英特爾、臺積電以及三星都是該技術的關鍵參與者,其中英特爾計劃2024年在2 nm制程中實施其背面供電技術“PowerVIA”,而臺積電則計劃2026年在2 nm制程的大批量生產中實施該項技術,另外三星也預計把該技術納入其2 nm制程中。

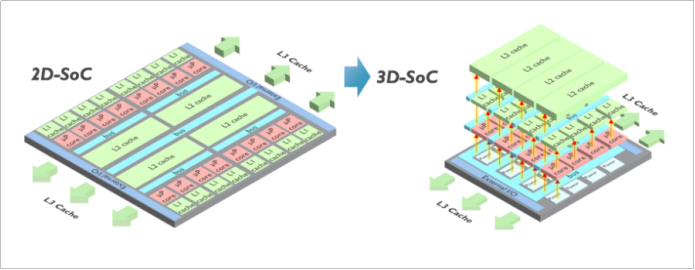

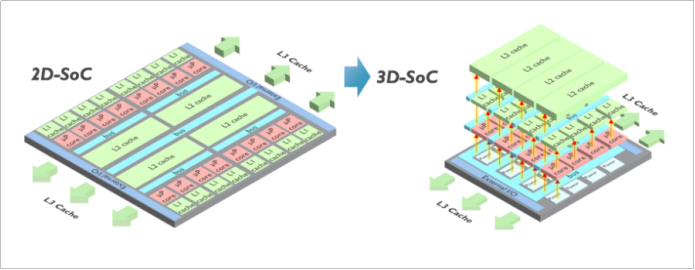

CMOS 2.0是IMEC在該活動上重點介紹的一項技術,該技術很大程度上依賴于BPDN技術。CMOS 2.0旨在將芯片分解成更小的部分,如將緩存和存儲器分解成不同單元,然后再將各小芯片進行3D堆疊排列。3D芯片設計實際上已經推出,例如AMD的第二代3D V-Cache(將L3內存堆疊在處理器上,以提高內存容量)。IMEC希望將該結構提高到一個新的水平,將L1、L2、L3緩存垂直堆疊在處理器上。雖然3D堆疊可以實現更高的緩存,緩解相關的延遲問題,同時也應注意將造成更高的成本。

圖8. 3D堆疊SoC(system on chip)將儲存、邏輯、I/O等功能分區