1

科研動(dòng)態(tài)

1、IEEE T. Comp. Pack. Man.:2.5D集成封裝嵌入式微通道散熱器研究

研究人員普遍認(rèn)為,溫度完整性是開(kāi)發(fā)2.5D/3D集成封裝系統(tǒng)最具挑戰(zhàn)性的障礙之一。

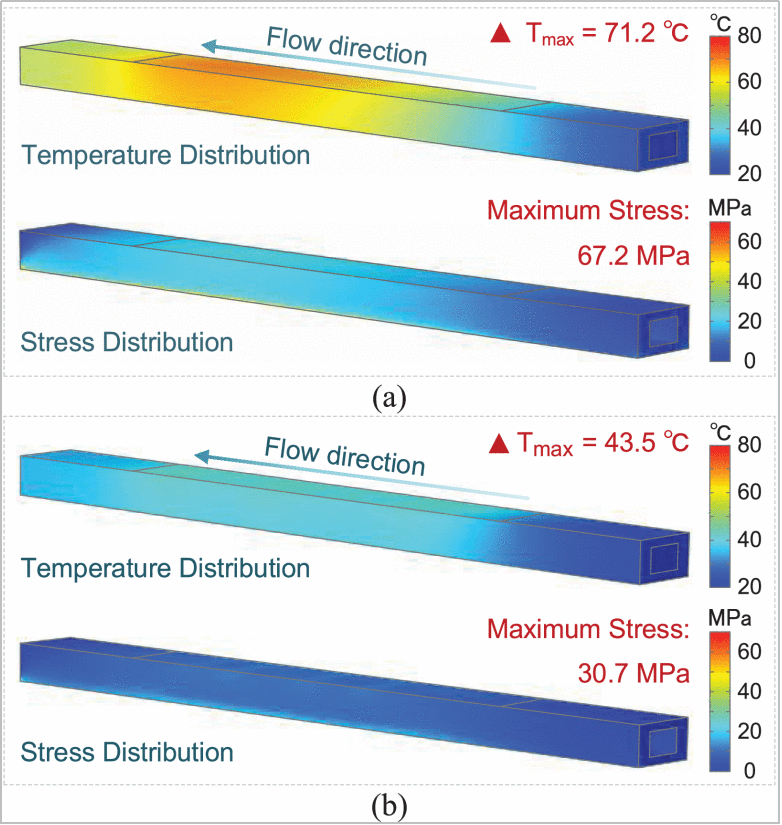

近日,浙江省大規(guī)模集成電路設(shè)計(jì)重點(diǎn)實(shí)驗(yàn)室的研究人員設(shè)計(jì)了一種用于2.5D封裝熱管理、帶有硅通孔(TSV)蝕刻微引腳鰭片的嵌入式微通道散熱器(EMCHS),并開(kāi)發(fā)數(shù)值模擬模型來(lái)估計(jì)EMCHS和封裝的熱性能和機(jī)械性能。首先驗(yàn)證了模型的準(zhǔn)確性,然后提出了一些模型簡(jiǎn)化手段以降低模型的階數(shù),從而提高仿真計(jì)算的時(shí)間并節(jié)省資源成本。通過(guò)進(jìn)一步在功率和散熱能力之間權(quán)衡,提出了一種EMCHS的最佳設(shè)計(jì)方法。該方法采用灰色關(guān)系分析來(lái)尋求最優(yōu)設(shè)計(jì)參數(shù),并采用仿真模型進(jìn)行快速性能評(píng)估。仿真結(jié)果表明,優(yōu)化后的EMCHS和2.5D封裝在散熱能力和機(jī)械可靠性方面均有顯著提高。該工作對(duì)2.5D集成封裝的散熱設(shè)計(jì)提供了參考。該文章以“Investigation on Embedded Microchannel Heatsink for 2.5-D Integrated Package”發(fā)表于IEEE T. Comp. Pack. Man.上。

圖1. 單個(gè)微通道的溫度與應(yīng)力分布:(a)不具有、(b)具有優(yōu)化排列的微引腳

論文鏈接:DOI:10.1109/TCPMT.2023.3292005

2、J. Appl. Polym. Sci.:用于柔性覆銅板的具有高剝離強(qiáng)度和優(yōu)異焊接耐熱性能的環(huán)氧膠粘劑

柔性覆銅板(FCCL)通常由銅箔、環(huán)氧粘合劑和聚酰亞胺(PI)薄膜組成,被廣泛用作柔性印刷電路板的基板材料。

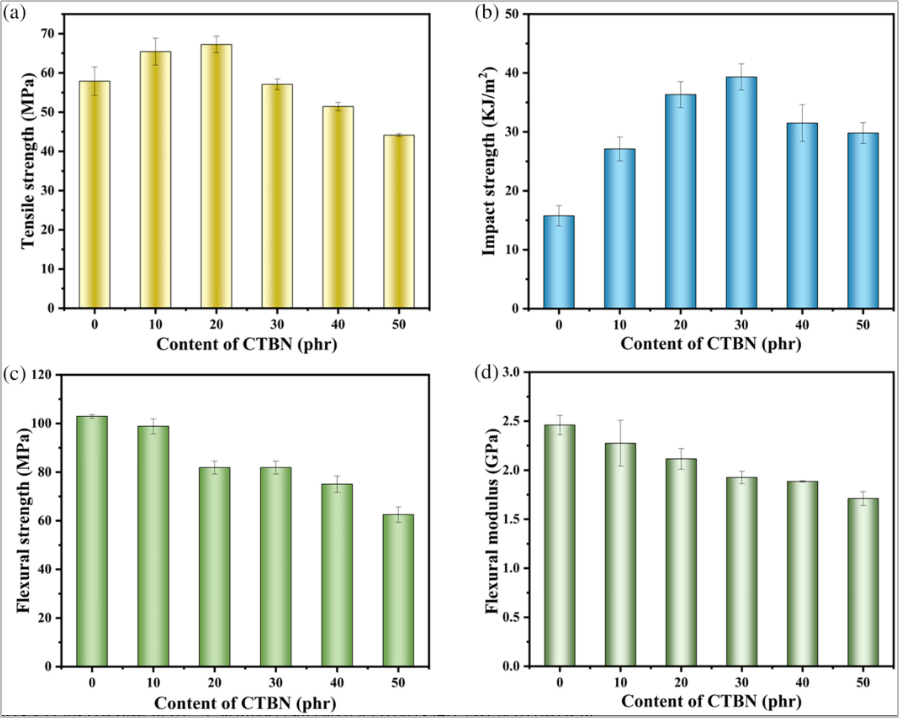

近日,華南理工大學(xué)的研究人員采用羧基封端丙烯腈-丁二烯(CTBN)和四種固化劑制備了改性環(huán)氧膠粘劑,并且用等離子體處理PI,以提高FCCL的剝離強(qiáng)度。結(jié)果表明,當(dāng)環(huán)氧膠黏劑加入30份的CTBN進(jìn)行增韌、PI薄膜用氮等離子體處理后,改性環(huán)氧膠粘劑和FCCL的綜合性能最好。改性環(huán)氧膠粘劑的沖擊強(qiáng)度為39.32?kJ?m?2(比未改性的高149.7%),160℃下凝膠化時(shí)間為330 s?。FCCL的剝離強(qiáng)度為1.29?kgf?cm?1,高于指標(biāo)要求。該方法為擴(kuò)展FCCL在需要更高剝離強(qiáng)度領(lǐng)域的應(yīng)用提供了一種新途徑。該文章以“High peel strength and excellent solder heat-resistance epoxy adhesive for flexible copper clad laminate”發(fā)表于J. Appl. Polym. Sci.上。

圖2. 不同CTBN含量改性的環(huán)氧膠粘劑的機(jī)械性能:(a)拉伸強(qiáng)度,(b)沖擊強(qiáng)度,(c)彎曲強(qiáng)度,(d)彎曲模量。

論文鏈接:https://doi.org/10.1002/app.54596

3、 Mat. Sci. Semicon. Proc.:關(guān)于TSV絕緣襯里替代材料的綜述

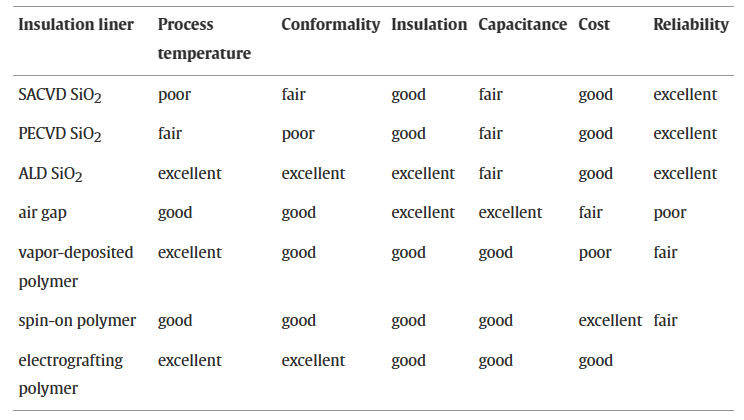

現(xiàn)今,3D集成是芯片領(lǐng)域被公認(rèn)的最有發(fā)展前景的方向。3D集成背后的核心技術(shù)是硅通孔(TSV)結(jié)構(gòu),它為芯片提供垂直電氣互連。絕緣襯里是保證TSV功能的關(guān)鍵部件,對(duì)電氣特性和熱機(jī)械可靠性產(chǎn)生重要影響。然而,由于集成和封裝形式趨于復(fù)雜化,傳統(tǒng)絕緣襯里面臨著持續(xù)的挑戰(zhàn),因?yàn)?/span>TSV的直徑變得更小、縱橫比變得更高。因此,需要不斷探索和測(cè)試新型絕緣襯里方法,以滿(mǎn)足嚴(yán)格的要求。

近日,上海交通大學(xué)的研究人員發(fā)表綜述文章,對(duì)絕緣襯里進(jìn)行了全面的比較和總結(jié),包括次常壓化學(xué)氣相沉積(SACVD)和等離子體增強(qiáng)化學(xué)氣相沉積(PECVD)等傳統(tǒng)方法,以及原子層沉積(ALD)、氣隙(air-gap)、氣相沉積聚合物和濕沉積聚合物等新型替代方法。根據(jù)其特定的性能特性(例如覆蓋性、電氣特性和熱機(jī)械可靠性)討論了每種方法的優(yōu)缺點(diǎn),這些性能對(duì)與TSV實(shí)現(xiàn)正常功能至關(guān)重要。對(duì)不同絕緣襯里的評(píng)估將有助于研究人員更好地理解這些方法,并根據(jù)他們的特定需求和要求做出合理決策。該綜述以“Alternative insulation liners for through-silicon vias: A comprehensive review”???表于Mat. Sci. Semicon. Proc.上。

表1. 不同絕緣襯里工藝的比較

論文鏈接:https://doi.org/10.1016/j.mssp.2023.107726

4、J. Electron. Packaging:電子封裝中多尺度結(jié)構(gòu)彈塑性問(wèn)題的自動(dòng)有限元法-邊界元法耦合方法

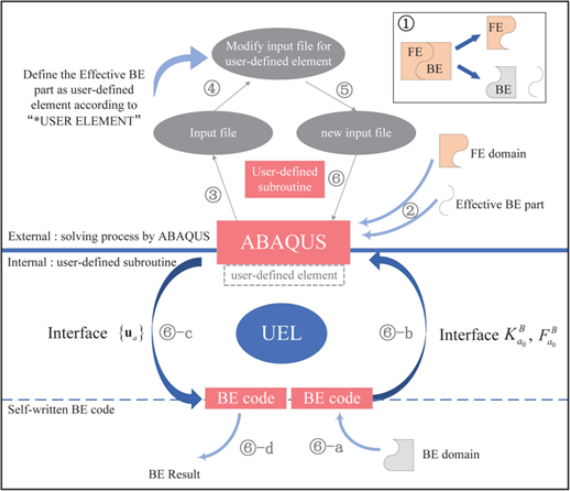

有限元在電子封裝結(jié)構(gòu)的仿真分析中起著重要作用。然而,由于電子封裝中的多尺度結(jié)構(gòu),數(shù)值模型必須離散化成大量的單元,以確保計(jì)算精度,這無(wú)疑增加了計(jì)算時(shí)間和成本。為了解決這個(gè)問(wèn)題,研究人員擴(kuò)展了邊界元方法,用于分析電子封裝問(wèn)題。

近日,北京科技大學(xué)等機(jī)構(gòu)的研究人員介紹了一種用于多尺度電子封裝結(jié)構(gòu)彈塑性分析的有限元和邊界元耦合方法。基于有限元-邊界元(FE-BE)耦合算法,開(kāi)發(fā)了一種針對(duì)彈性問(wèn)題,自動(dòng)實(shí)現(xiàn)ABAQUS(一種有限元模擬軟件)與自寫(xiě)彈性BE碼耦合的程序。首先,在有限元-邊界元混合模型中,采用自行編寫(xiě)的BE程序?qū)缑嫣幍挠行偠群陀行ЯM(jìn)行了評(píng)估。然后,使用ABAQUS中的用戶(hù)子程序(UEL)將獲得的有效剛度和有效力組裝成全局有限元公式。有限元理論可以對(duì)具有塑性變形、應(yīng)力集中等情況的結(jié)構(gòu)進(jìn)行數(shù)值模擬,邊界元法適用于具有大型結(jié)構(gòu)的線彈性域。與目前可用于多尺度電子封裝結(jié)構(gòu)的分析方法相比,該方法具有以下幾個(gè)關(guān)鍵優(yōu)勢(shì):(1)ABAQUS強(qiáng)大的前處理和后處理能力;(2)精度更高;(3)減少計(jì)算成本和時(shí)間;(4)可通過(guò)使用邊界元作為補(bǔ)充來(lái)求解具有無(wú)限可拓性的系統(tǒng)。該方法被證明可以處理電子封裝中多尺度結(jié)構(gòu)的相關(guān)問(wèn)題。該文章以“An Automatic Finite Element Method-Boundary Element Method Coupling Method for Elastic–Plastic Problems of Multiscale Structures in Electronic Packaging”發(fā)表于J. Electron. Packaging上。

圖3. 耦合方案流程圖

論文鏈接:https://doi.org/10.1115/1.4055125

2

技術(shù)動(dòng)態(tài)

1、近期Chiplet和異構(gòu)集成的進(jìn)展和趨勢(shì)

摩爾定律正逼近物理極限,減小片上系統(tǒng)(SoC)的特征尺寸變得越來(lái)越困難,且成本高昂。近年來(lái),國(guó)際巨頭們均著力于發(fā)展Chiplet設(shè)計(jì)和異構(gòu)集成封裝技術(shù),即把SoC劃分成不同的功能區(qū)域,實(shí)現(xiàn)更好性能的同時(shí)減少成本。

(1)AMD

2017年,加州大學(xué)圣芭芭拉分校與ADM公司發(fā)表論文,展示了AMD未來(lái)的chiplet設(shè)計(jì)和異構(gòu)集成封裝,即小芯片通過(guò)TSV中介層堆疊在一起,形成一種3D集成。

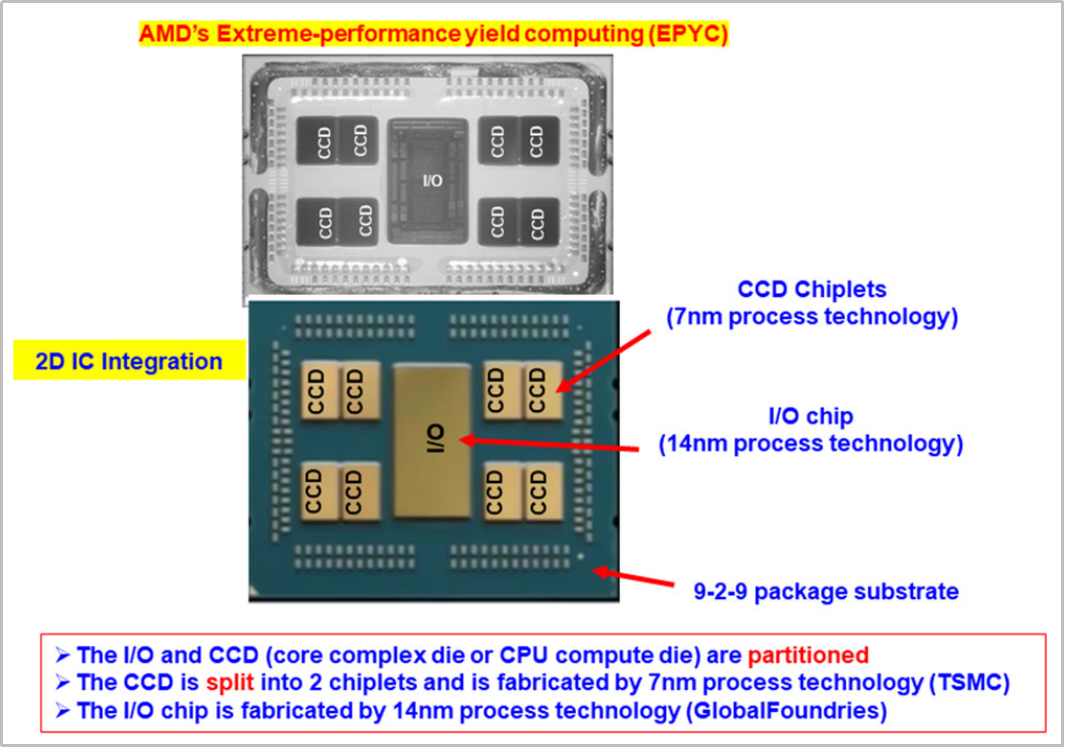

a)EPYC(Extreme-Performance Yield Computing)

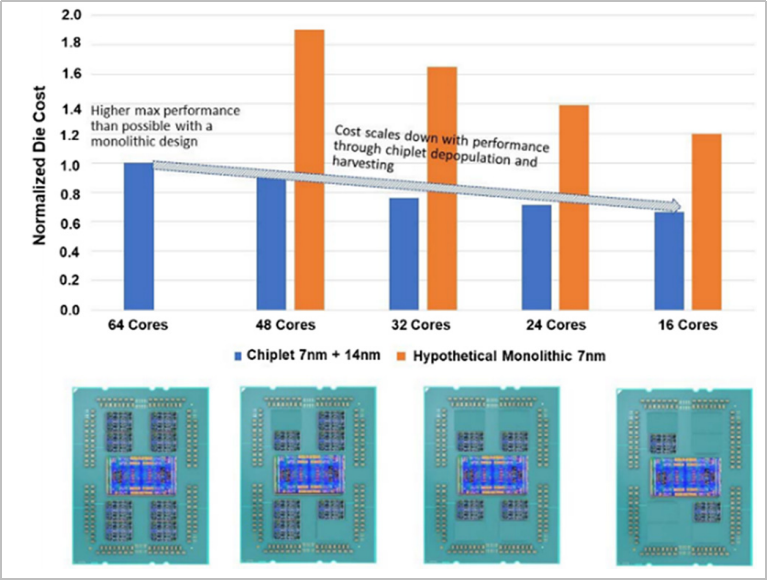

對(duì)于高性能服務(wù)器和處理器等I/O的密度十分高的場(chǎng)景,先進(jìn)制程對(duì)于提高I/O密度十分有限且造價(jià)昂貴。2019年年中,AMD推出了第二代EPYC 7200系列,代號(hào)為Rome,核心數(shù)量增加到64個(gè),如圖4所示,該技術(shù)采用一種9-2-9封裝,I/O和CPU分別被分為多個(gè)小芯片,CPU核心采用7 nm制程,I/O芯片采用14 nm制程。AMD保持封裝尺寸和引腳排列不變,同時(shí)核心數(shù)量從第一代的4個(gè)增加到第二代的9個(gè),因此需要更緊密的芯片/封裝的協(xié)同設(shè)計(jì)。

第二代EPYC的性能與成本對(duì)比如圖5所示,核心數(shù)量越多意味著成本更高,但是采用chiplet設(shè)計(jì)能節(jié)約近一半的成本,隨著核心數(shù)量增多,chiplet設(shè)計(jì)的成本優(yōu)勢(shì)越發(fā)明顯。

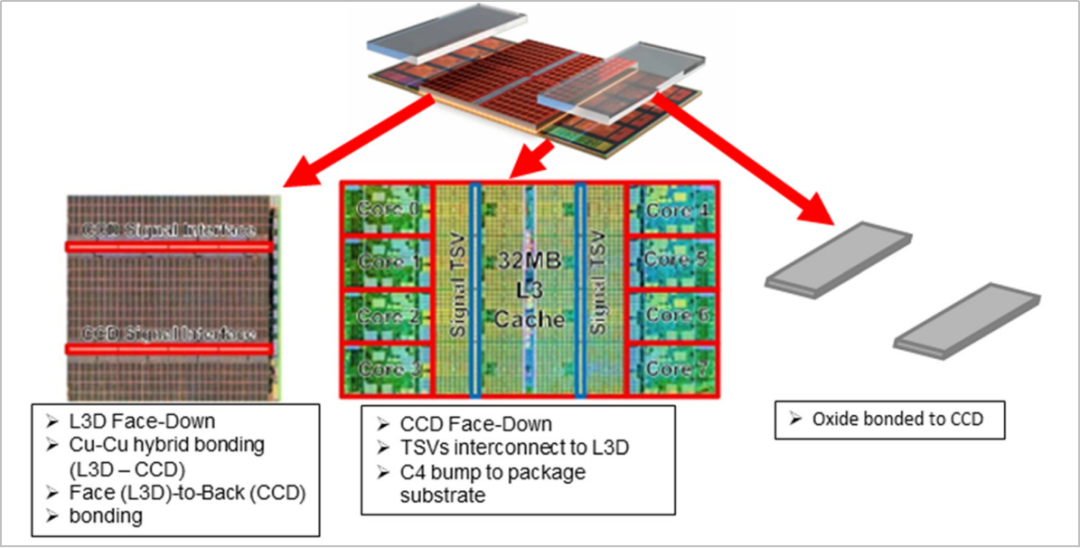

b)AMD 3D V-Cache

在2022年,AMD發(fā)布了他們的3D V-Cache chiplet設(shè)計(jì),如圖6所示。該結(jié)構(gòu)由底部的計(jì)算芯片、頂部的靜態(tài)RAM和用于平衡結(jié)構(gòu)并提供散熱路徑的結(jié)構(gòu)芯片組成。底部計(jì)算芯片是采用臺(tái)積電7 nm工藝技術(shù)制造的“Zen 3”CPU,頂部是同樣由7 nm工藝制造的擴(kuò)展L3芯片。頂部芯片面朝下與底部芯片通過(guò)Cu-Cu混合鍵合。

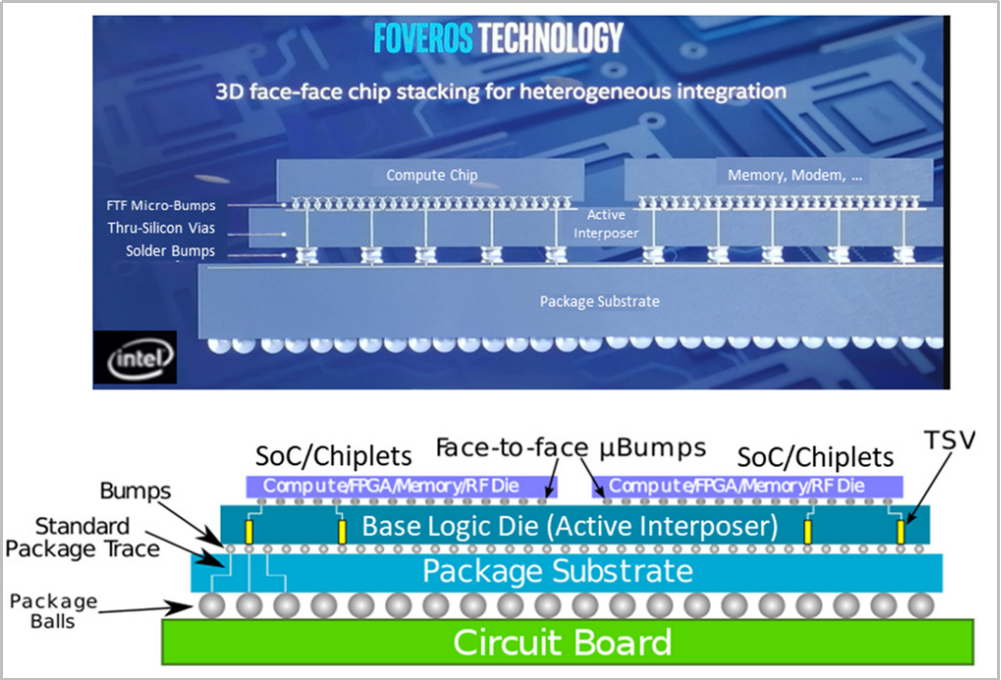

a)Intel’s Foveros技術(shù)

Intel在2018年12月和2019年7月分別發(fā)布了Foveros技術(shù)和全向互聯(lián)(ODI)技術(shù),如圖7所示。TSV中介層是帶有CMOS(互補(bǔ)金屬氧化物半導(dǎo)體)器件(有源中介層),有源TSV中介層位于SoC或chiplet的下方,與小芯片或SoC通過(guò)熱壓鍵合。

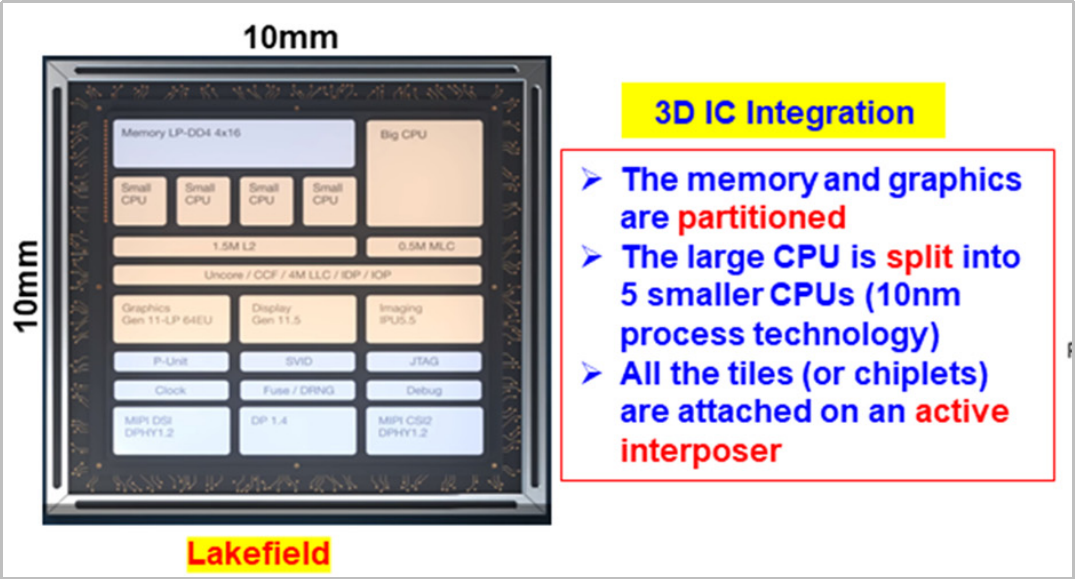

b)Intel’s Lakefield

2020年7月,基于Foveros技術(shù),英特爾推出筆記本電腦處理器“Lakefield”。如圖8所示,SoC被劃分為CPU、GPU、LPDDR4等多個(gè)部分,并且CPU繼續(xù)被分割成1大+4小CPU,然后使用CoW(chip on wafer)工藝使小芯片面對(duì)面鍵合(堆疊)在有源TSV中介層。小芯片是10 nm工藝制造,基底芯片采用22 nm工藝。這是首個(gè)大批量制造的3D chiplet集成,并用于筆記本電腦等移動(dòng)產(chǎn)品。

圖8. Intel’s Lakefield示意圖

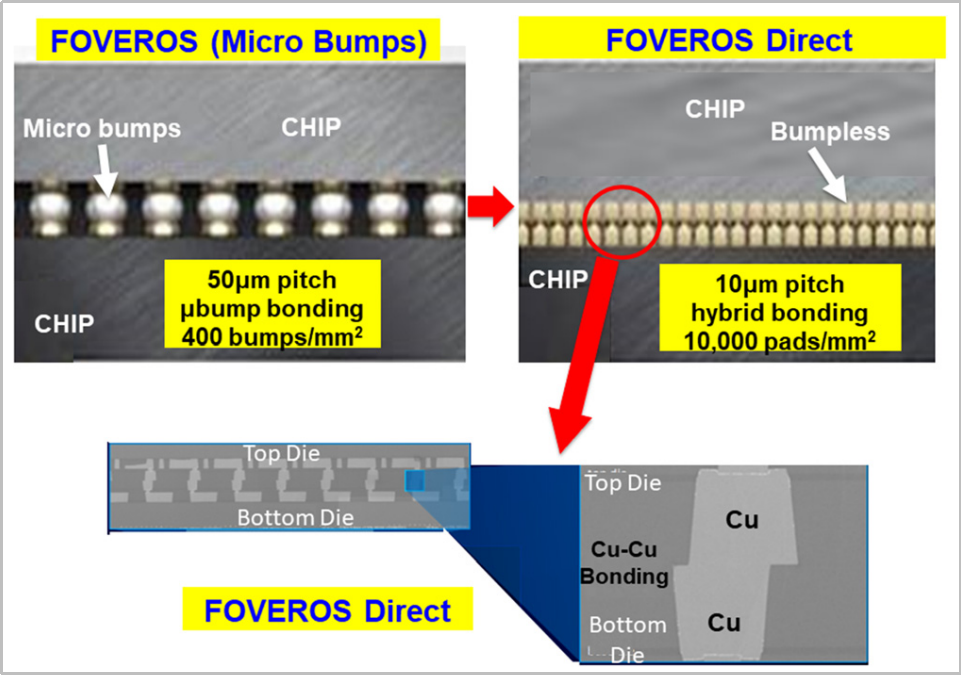

c)Intel’s Foveros-Direct

2020年8月13日,Intel發(fā)布采用Cu-Cu鍵合的Foveros-Direct技術(shù)。通過(guò)混合鍵合代替凸塊,可將間距從Lakefield的50 μm降至10 μm。

圖9. Intel’s Foveros-Direct(Cu-Cu混合鍵合)

(3)臺(tái)積電

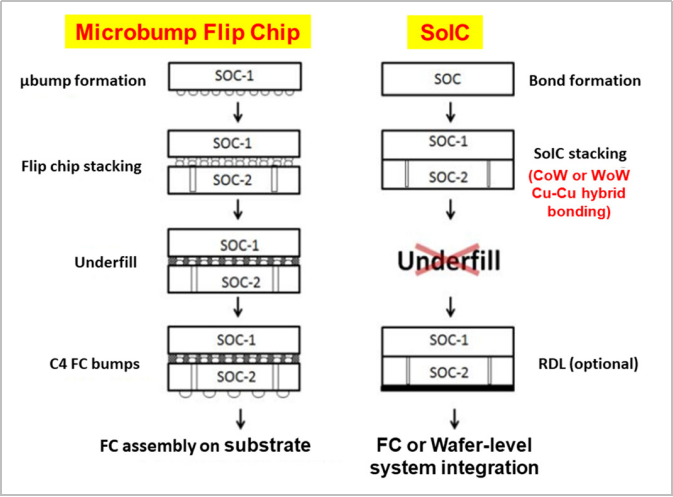

a)3D Fabric

2020年8月,臺(tái)積電宣布了他們的3D Fabric技術(shù),可應(yīng)用于手機(jī)、高性能計(jì)算、汽車(chē)和物聯(lián)網(wǎng)等領(lǐng)域。3D Fabric的核心技術(shù)是SoIC(system on integrated chips),該技術(shù)由臺(tái)積電于2018年發(fā)布。3D Fabric可以通過(guò)CoW(chip on wafer)和WoW(wafer on wafer)提供靈活的芯片級(jí)chiplet設(shè)計(jì)和集成,與傳統(tǒng)微凸塊鍵合相比,混合鍵合SoIC具有更好的電氣性能和密度,以及更好的熱性能。

圖10. 臺(tái)積電SoIC與倒裝封裝對(duì)比

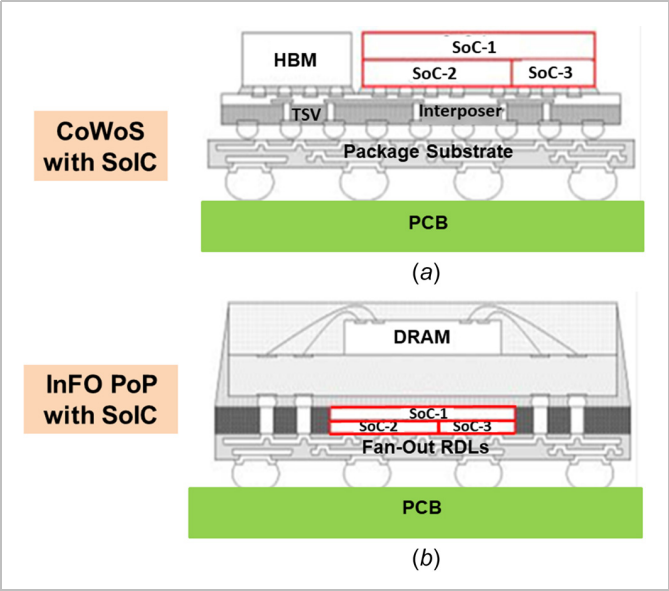

b)臺(tái)積電CoWoS和InFO POP

在3D后端集成方面,CoWoS(chip on wafer on substrate)封裝技術(shù)提供了極高的計(jì)算性能和高寬帶內(nèi)存,可滿(mǎn)足高端服務(wù)器的高速運(yùn)算需求;InFO(集成扇出)提供了存儲(chǔ)器-邏輯、邏輯-邏輯、PoP(package-on-package)等應(yīng)用。

圖11. 在異構(gòu)集成前,使用SoIC進(jìn)行小芯片的堆疊(a)采用SoIC的CoWos、(b)采用SoIC的InFO PoP

4. Chiplet設(shè)計(jì)和異質(zhì)集成封裝的優(yōu)缺點(diǎn)

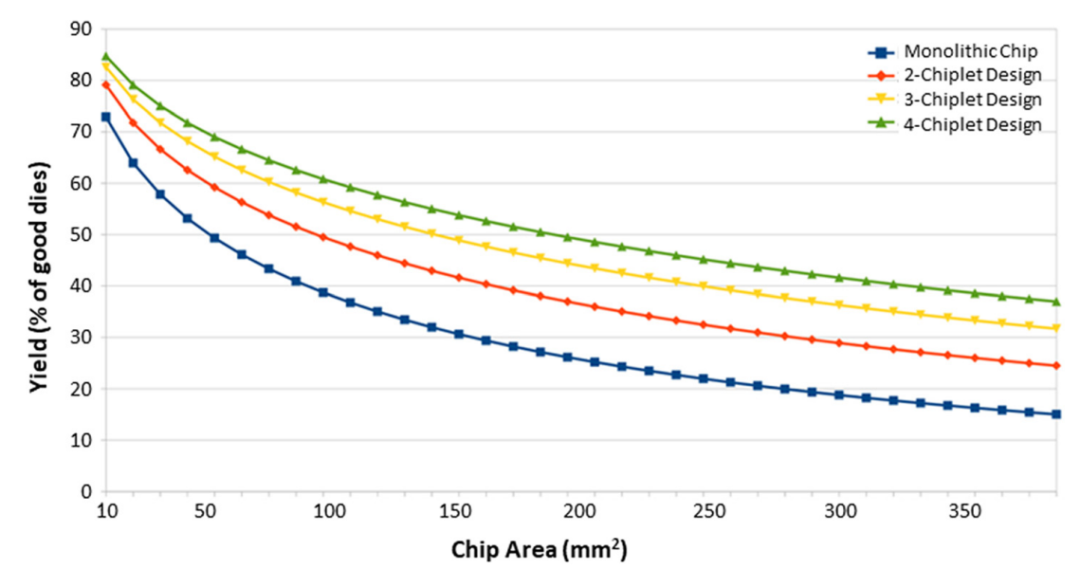

與SoC相比,chiplet設(shè)計(jì)的主要優(yōu)勢(shì)在于可以提高良率、降低成本。圖12顯示了整片設(shè)計(jì)和分別拆分成2、3、4個(gè)小芯片的整體芯片產(chǎn)量比較。可以看出芯片尺寸越小,良率就越高,最終產(chǎn)量提高,從而可以轉(zhuǎn)化為更低的成本,同時(shí)加快產(chǎn)品迭代時(shí)間。此外,由于分散成小芯片,可以提高整體的散熱效率。

圖12. 芯片整體良率與芯片尺寸的關(guān)系

然而,由于芯片分區(qū),毫無(wú)疑問(wèn)將增大芯片面積,因此反過(guò)來(lái)對(duì)封裝整體設(shè)計(jì)提出更高要求,以實(shí)現(xiàn)更小體積。同時(shí),chiplet要求更多、更高密度的封裝互聯(lián),對(duì)封裝材料提出了更高的要求。

(Source:John H. Lau, Recent Advances and Trends in Chiplet Design and Heterogeneous IntegrationPackaging, ASME Journal of Electronic Packaging, Vol 146, 010801, 2024.)