在隨著對電子設備性能要求的不斷提升,傳統的單芯片封裝方式已經無法滿足市場對于高密度、高性能、小尺寸的需求。因此,芯粒封裝技術應運而生,成為集成電路領域的關鍵創新點。

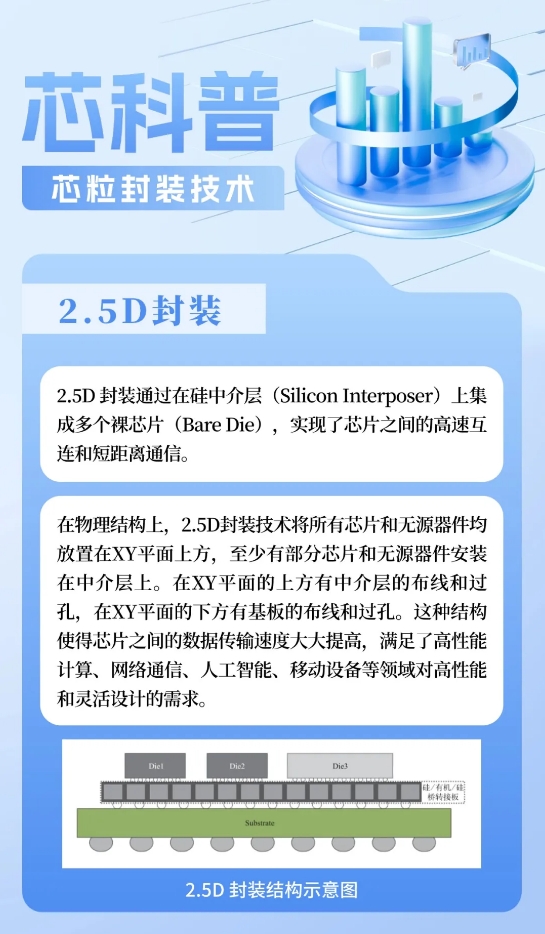

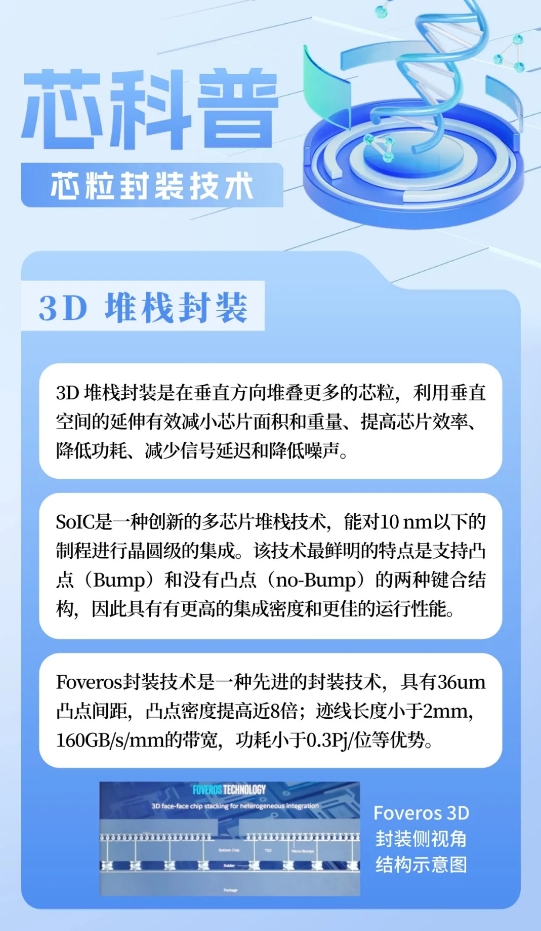

芯粒封裝技術,作為集成電路領域的一項創新,提供了一種全新的解決方案。它通過優化芯片的布局和連接方式,實現了更高的集成度和更優的性能表現。這些技術包括但不限于MCM封裝技術、2.5D封裝技術、3D堆棧封裝技術以及3D FO封裝技術,每一種都以其獨特的方式推動了電子設備的性能極限。

接下來,我們講對這四種芯粒封裝技術進行講解。

芯粒集成技術,以其突破性的創新,為半導體產業帶來了新的生機。盡管目前仍處于發展階段,但它在提升芯片性能和集成度方面的潛力已經初露端倪。隨著技術的成熟和市場的拓展,我們期待芯粒技術能夠在算力大模型時代發揮關鍵作用,推動半導體產業邁向更高峰。讓我們拭目以待,這一技術如何在未來塑造我們的數字世界。

參考來源:

1.馬鵬.芯粒集成技術研究進展[J].焦作大學學報,2024,38(03):62-67.

2.王成遷,湯文學,戴飛虎,等.面向大算力應用的芯粒集成技術[J].電子與封裝,2024,24(06):48-53.

3.英特爾Foveros 3D封裝技術,https://mp.weixin.qq.com/s/lQUzhOj1Cr-vKm9nWjzalA

4.3D芯片SiP與POP堆疊封裝技術,https://mp.weixin.qq.com/s/B6iRSI2EmGnbxbUE4Evq6g

來源:文化宣傳辦

審核:吳曉琳