1 電介質材料

1、Nature Materials :高熵增強電容儲能

靜電介質電容器由于其超快的充放電速度和高功率密度,是先進電子和電力系統中必不可少的元件。然而,如何提高它們的能量密度,以滿足下一代應用對小型化、集成化的需求,已成為當前的主要挑戰。

最近,清華大學等機構的研究人員報道了一種高熵穩定的Bi2Ti2O7基介電薄膜,其在6.35 MV cm-1電場下的能量密度高達182?J?cm?3,效率為78%?。研究表明,調節原子構型熵可以引入有利且穩定的微觀結構特征,包括晶格畸變的納米晶粒和無序的類非晶相,能夠提高擊穿強度并減少極化反轉遲滯,從而協同提高儲能性能。這種高熵方法有望廣泛應用于高性能電介質材料的開發。該研究成果以“High-entropy enhanced capacitive energy storage”發表于Nature Materials上。

圖1. 高熵薄膜中的晶格畸變、納米晶粒和無序的類非晶相可協同提高儲能性能

論文鏈接:https://www.nature.com/articles/s41563-022-01274-6

2、J. Mater. Chem. A:同時具有大能量密度和高效率的介質電容器用NaNbO3-(Sr,Bi)TiO3-Bi(Mg,Zr)O3弛豫鐵電陶瓷

高性能電介質材料是多層陶瓷電容器(MLCC)的關鍵材料,特別是先進儲能、脈沖功率技術的快速發展,對其提出了迫切需求。然而,在一種材料中同時實現高儲能密度(Wrec)和高效率(η)仍然是一個挑戰。

最近,中國科學院上海硅酸鹽研究所等機構的研究人員基于疇結構和帶隙工程設計了一種新型的NaNbO3基0.88(0.85NaNbO3-0.15Sr0.7Bi0.2TiO3)-0.12Bi(Mg0.5Zr0.5)O3 (NN-SBT-BMZ)弛豫鐵電陶瓷。通過NN-SBT-BMZ復合固溶體的形成,實現了無序度的提高和固有電子帶隙的增加。這種材料表現出增強的極化-電場線性關系和擊穿強度,同時獲得了7.59 J/cm3的超高儲能密度和81.3%的高儲能效率,并顯示出優異的溫度穩定性(超寬溫度范圍-120℃-180℃)、頻率穩定性(10-150 Hz)和循環穩定性(最多106個循環)。此外,充放電測試表明,樣品具有優異的功率密度(76.78 MW/cm3),超快的放電速率(t0.9~35 ns),在介質電容器領域具有潛在應用前景。相關研究工作以“Simultaneously achieving large energy density and high efficiency in NaNbO3-(Sr,Bi)TiO3-Bi(Mg,Zr)O3 relaxor ferroelectric ceramics for dielectric capacitor applications”發表于J. Mater. Chem. A上。

圖2. 同時具有大能量密度和高效率的弛豫鐵電陶瓷

論文鏈接:https://doi.org/10.1039/D2TA01808J

2 熱管理材料

1、Chem. Eng. J. :受壁虎啟發的粘合結構能夠在高度不匹配的系統中有效地實現熱導和振動耗散

聚合物基熱界面材料(TIM)的熱導率和振動耗散之間往往存在權衡。實現有效的熱管理需要足夠高的填料含量,然而,這會反過來增加TIM的儲能模量,從而影響其阻尼性能。

最近,受自然界壁虎攀爬的啟發,深圳先進電子材料國際創新研究院的研究人員設計了一種具有豐富短懸掛的梳刷狀共聚物,可以適應組成材料(TIM/基板)和復合材料內部(聚合物/填料)高度不匹配的界面。實驗表明,調整梳刷狀共聚物的重量比可獲得最佳的導熱系數(4.9±0.1 W·m?1·K?1)和接觸熱阻(0.2±0.05 K·cm2·W?1)。此外,聚合物/填料之間范德華相互作用的解離和展寬的弛豫譜有效地耗散了振動能量,使TIM在較寬的頻率范圍(>0.5 Hz)內具有優異的阻尼能力。這項研究為下一代高性能TIMs的開發指出了一個有希望的方向,在智能互聯汽車領域有潛在應用價值。研究論文以“Gecko-inspired adhesive structures enable efficiently thermal conductance and vibration dissipation in a highly mismatched system”發表于Chem. Eng. J.上。深圳先進電子材料國際創新研究院熱管理材料研究中心博士后范劍鋒為第一作者,任琳琳副研究員為通訊作者。

圖3. 受壁虎啟發的粘合結構能夠在高度不匹配的系統中有效地實現熱導和振動耗散

論文鏈接:https://doi.org/10.1016/j.cej.2022.136754

3 電磁屏蔽材料

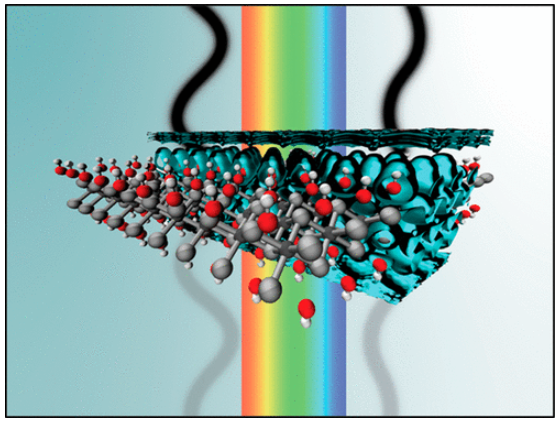

1、ACS Nano :具有優異透明電磁屏蔽性能的2D單層膜

隨著無線通信技術的快速發展,需要能夠選擇性地允許可見光傳輸并防止低頻GHz電磁干擾(EMI)的材料。盡管石墨烯、過渡金屬二鹵化物和MXenes等2D材料顯示出此類應用的前景,但具有較高可見光透過率(Tvis)和屏蔽效能(SE)的2D單層膜方面的進展甚微。由于結構和成分的多變性,二維材料空間太大,無法進行系統的實驗研究。

為了應對上述挑戰,MIT的研究人員進行了高通量計算篩選。利用原子第一性原理方法,同時計算了7000種2D單層材料的Tvis和SE,從中發現26種單層材料具有>98% Tvis和>5 dB SE的優異性能(約70% EMI衰減)。研究團隊首選了AgSe2單層材料,預測其Tvis為98.53%,SE為12.53 dB(約94% EMI衰減),比目前最先進的石墨烯性能更好(Tvis=96.7%,SE=3.04 dB)。此外,研究團隊還深入分析了這種2D單層膜的透明EMI屏蔽性能及其電子結構,并闡明了表面終端和近自由電子態的作用。該研究成果以“2D Monolayers for Superior Transparent Electromagnetic Interference Shielding”發表于ACS Nano上。

圖4. 具有優異透明電磁屏蔽性能的2D單層膜

論文鏈接:https://doi.org/10.1021/acsnano.2c02556

4 熱電材料

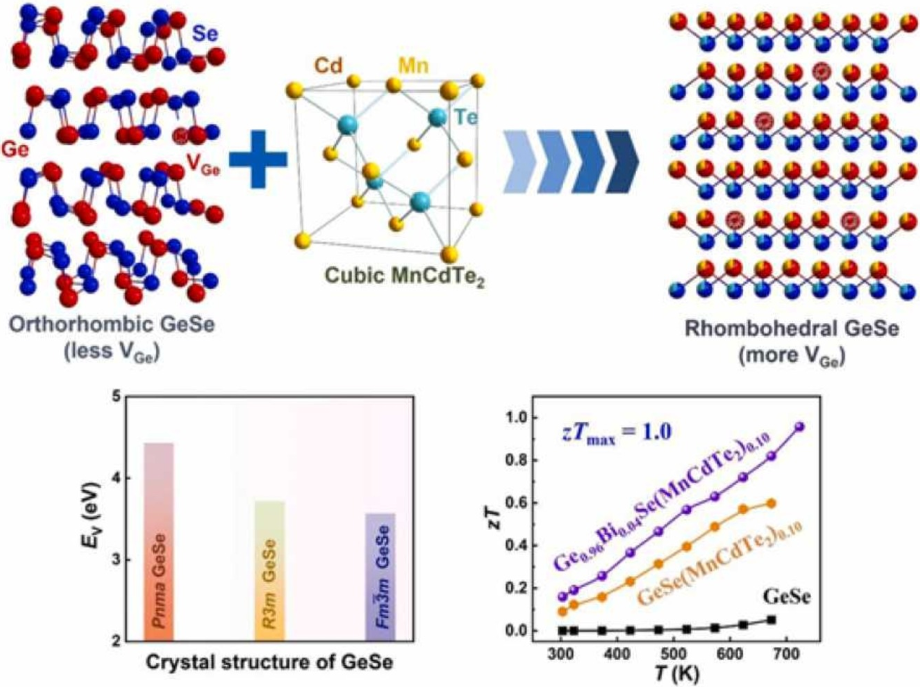

1、Nano Energy :晶體對稱性使六方GeSe(MnCdTe2)x具有高熱電性能

高對稱性有利于獲得高功率因數,然而,晶體對稱性在提高材料熱電性能方面的作用尚不十分明晰。

近期,深圳大學等機構的研究人員利用晶體對稱性和本征點缺陷之間的相互作用成功實現了IV-VI半導體GeSe的高zT。由于Ge空位的形成能較高,原始正交GeSe的zT值較低(約0.05),因而載流子濃度較低(約1016 cm?3)。用MnCdTe2合金化GeSe可以穩定高對稱性的六方結構,從而有效地降低Ge空位的形成能,并將載流子濃度提高四個數量級。同時,與正交GeSe相比,六方Ge1-yBiySe(MnCdTe2)x具有更高的谷簡并度和更小的帶有效質量,使得Seebeck系數和載流子遷移率更大。體系中生成的多尺度微結構,包括原子尺度的本征Ge空位和取代點缺陷、納米尺度的疇結構和微米尺寸的第二相,均有效降低了晶格熱導率。Ge0.96Bi0.04Se(MnCdTe2)0.10在723 K時達到了~1.0的zT值。這些結果證明了晶體對稱性和本征點缺陷之間的相互作用在獲得高性能GeSe基和其他熱電材料方面的有效性。該研究工作以“Crystal symmetry enables high thermoelectric performance of rhombohedral GeSe(MnCdTe2)x”發表于Nano Energy上。

圖5. 晶體對稱性使六方GeSe(MnCdTe2)x具有高熱電性能

論文鏈接:https://doi.org/10.1016/j.nanoen.2022.107434

5 電子封裝材料

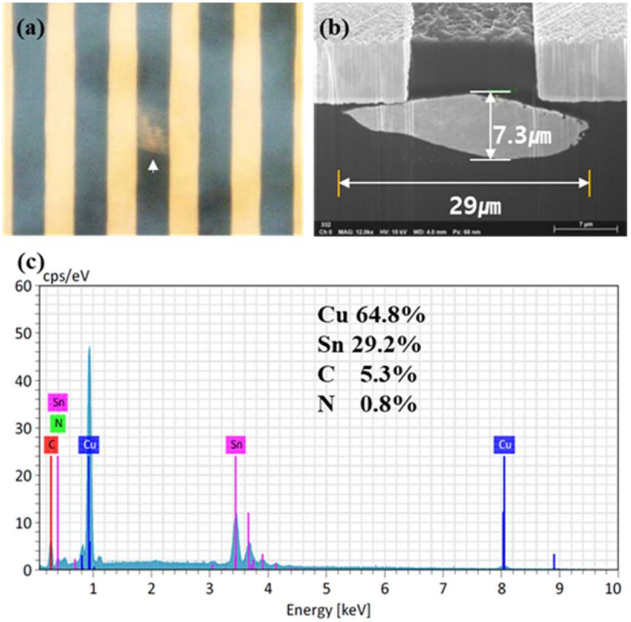

1、IEEE Trans. Comp. Pkg. Man. Tech.:顯示驅動芯片COF封裝中金屬粒子的介電擊穿

電氣測試是檢測顯示驅動IC(DDI)COF(Chip-on-Flex)封裝制造中電氣故障的最后一步。

近日,韓國三星電子等機構的研究人員報道了幾個案例,在顯示測試或面板級老化測試期間,通過直流電測試證明良好的COF封裝后來發生了電氣短路。聚焦離子束(FIB)橫截面分析表明,在有缺陷的COF封裝中,兩條導線之間存在金屬顆粒。在導線和金屬顆粒之間存在填充了底部填充材料的亞微米間隙,間隙大小從50 nm到500 nm不等。間隙底部填充層中存在空隙、分層和裂紋。結果表明,在顯示測試期間,導線和金屬顆粒之間亞微米間隙中的底部填充材料在高電場下降解,并最終因介電擊穿而短路。相關研究內容以“Dielectric Breakdown by Metallic Particles in COF Packaging for Display Driver IC”發表于IEEE Trans. Comp. Pkg. Man. Tech.上。

圖6. 失效COF封裝的圖像和元素分析

論文鏈接:DOI: 10.1109/TCPMT.2022.3176393

2、Chem. Eng. J. :新型雜化鋯-硅樹脂作為高溫膠黏劑及其耐熱機理研究

為了保證先進設備在高達1500℃的極端環境下的服役性能,迫切需要開發具有優異耐熱性的粘結材料。

最近,哈爾濱工業大學的研究人員通過在與烷氧基硅烷共聚縮合過程中添加正丙醇鋯(ZTP)作為結構控制組分,合成了一種新型雜化鋯-硅樹脂(ZAS樹脂),并提出了其高溫下結構晶體轉變相圖。Zr的加入顯著提高了材料的耐熱性。在1000℃氬氣氣氛下,殘余重量增加了168.2%,從最初的31.58%增加到84.71%。室溫下和1200℃燒蝕0.5h后,ZAS33樹脂的結合強度分別提高了296.1%和92.8%。該樹脂在至少6個月內具有優異的貯存穩定性,大大拓寬了其作為耐高溫粘接材料的應用前景。相關研究工作以“Novel hybrid zirconium-silicone resin as high-temperature adhesive and an insight into the thermal resistance mechanism”發表于Chem. Eng. J.上。

圖7. 可用作高溫膠黏劑的新型雜化鋯-硅樹脂材料

論文鏈接:https://doi.org/10.1016/j.cej.2022.137350

3、IEEE Trans. Comp. Pkg. Man. Tech.:RDL-First扇出型面板級封???的翹曲估計力學建模對比

為了滿足低成本、薄型化和多功能的要求,扇出型面板級封裝(fan-out panel-level packaging,FO-PLP)被引入到下一代封裝技術中。然而,在溫度循環過程中,FO-PLP的翹曲問題仍然是一個關鍵問題。因此,利用有限元分析(FEA)來估計FO-PLP的翹曲,并揭示翹曲誘導失效的主要機制至關重要。

近日,臺灣清華大學的研究人員提出了三種等效材料方法(零變形法、力平衡法和改進的Timoshenko雙材料法)以解決復雜RDL帶來的封裝翹曲計算瓶頸問題,并對其進行了比較。為了驗證這些方法,進行了實驗測量和模擬結果之間的翹曲比較。結果表明,由于對翹曲實際力學行為的可行假設,改進的Timoshenko方法對RDL-first FO-PLP翹曲的評估能力最好。對于等效材料的提取,基于仿真的材料測試方法更適合獲得等效RDL。當采用改進的Timoshenko雙材料方法與基于模擬的材料測試方法相結合時,預測的翹曲度在模擬和實驗之間只有0.9%的偏差。因此,通過所提出的仿真方法,可以準確估計FO-PLP中RDL引起的翹曲。該研究論文以“Comparison of Mechanical Modeling to Warpage Estimation of RDL-First Fan-Out Panel-Level Packaging”發表于IEEE Trans. Comp. Pkg. Man. Tech.上。

圖8. 完成整個多層RDL工藝之后的FO-PLP翹曲測量

論文鏈接:DOI: 10.1109/TCPMT.2022.3175953

4、IEEE Trans. Comp. Pkg. Man. Tech.:帶有2.5D硅通孔中介層的芯粒(Chiplet)封裝的熱學建模

基于芯粒的封裝技術將多個具有不同功能和材料的異質芯片集成到一個單一系統中,但它也給芯片的熱設計和芯粒之間的熱串擾帶來了新的挑戰。

近期,南京大學等機構的研究人員針對帶有2.5D硅通孔中介層的Chiplet基封裝進行了熱學建模。兩個芯粒被并排置于中介層上,銅蓋分別通過熱界面材料TIM1和膠黏劑連接到芯粒頂面和中介層外圍。為了進一步散熱,通過一層TIM2將熱沉連接到蓋子的頂面。對TIM類型、芯粒與中介層之間的鍵合方式、熱沉結構、熱串擾、蓋子上方的對流傳熱系數和熱設計功率(TDP)進行分析,發現無凸塊互連有利于芯粒封裝的散熱。短間距將為細間距多芯粒集成帶來冷卻挑戰,隨著蓋子上方對流傳熱系數的增加,溫度先迅速下降,然后減緩。在10000 W/m2K下,最大TDP約為250 W。相關研究內容以“Thermal Modeling of a Chiplet-Based Packaging with a 2.5D Through-Silicon Via Interposer”發表于IEEE Trans. Comp. Pkg. Man. Tech.上。

圖9. 芯片和蓋子之間界面熱阻示意圖

論文鏈接:DOI: 10.1109/TCPMT.2022.3174608

圖文 | 戰略研究辦公室

編輯 | 宣傳辦